CG-273-81

VOLUME I

11.12.

# **TECHNICAL MANUAL**

for

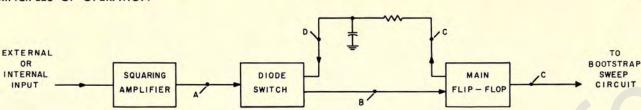

# LORAN RECEIVING SET AN/SPN-30

Sections 1 through 4

COLLINS RADIO COMPANY TEXAS DIVISION DALLAS, TEXAS

UNITED STATES COAST GUARD

COLLINS RADIO COMPANY TEXAS DIVISION DALLAS, TEXAS

# UNITED STATES COAST GUARD

Contract: Tcg-40907

Approved by U. S. Coast Guard November 1961

### RECORD OF CORRECTIONS MADE

| CHANGE NO. | DATE | FIELD CHANGE NO. | SIGNATURE |

|------------|------|------------------|-----------|

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            | •    |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

|            |      |                  |           |

ORIGINAL

#### UNITED STATES COAST GUARD

ADDRESS REPLY TO: C O M M A N D A N T U.S. COAST GUARD HEADQUARTERS WASHINGTON 25, D.C.

•EEE 20 November 1961

#### LETTER OF PROMULGATION

1. CG-273-81 is the Technical Manual for Loran Receiving Set Type AN/SPN-30 and is effective upon receipt. The two copies furnished with the equipments are parts thereof and shall accompany the basic equipment.

2. Extracts from this publication may be made to facilitate the preparation of other technical manuals and handbooks.

3. Copies of this publication may be obtained by requisition to Commanding Officer, U. S. Coast Guard Supply Center, Brooklyn, New York.

4. Corrections to this publication will be made by serially numbered amendments. They shall be entered promptly by responsible personnel.

Chief, Office of Engineering

| PAGE<br>NUMBERS | CHANGE IN<br>EFFECT | PAGE<br>NUMBERS           | CHANGE IN<br>EFFECT |

|-----------------|---------------------|---------------------------|---------------------|

| Volume I        |                     | Volume II                 |                     |

| Title Page      | Original            | Title Page                | Original            |

| ii to xii       | Original            | ii                        | Original            |

| 1-i             | Original            | 5-i to 5-v                | Original            |

| 1-0 to 1-8      | Original            | 5-0 to 5-270              | Original            |

| 2-i             | Original            | 6-i to 6-viii             | Original            |

| 2-0 to 2-10     | Original            | 6-1 to 6-258              | Original            |

| 3-i to 3-ii     | Original            | i-1 to i-18<br>Volume III | Original            |

| 3-1 to 3-30     | Original            | Title Page                | Original            |

| 4-i to 4-v      | Original            | ii                        | Original            |

| 4-0 to 4-130    | Original            | 7-i to 7-ii               | Original            |

|                 |                     | 7-1 to 7-506              | Original            |

### LIST OF EFFECTIVE PAGES

# LIST OF SECTIONS

#### Section

| 1 | General Information     | 1-0 |

|---|-------------------------|-----|

| 2 | Installation            | 2-0 |

| 3 | Operator's Section      | 3-1 |

| 4 | Principles of Operation | 4-0 |

| 5 | Troubleshooting         | 5-0 |

| 6 | Service and Repair      | 6-1 |

| 7 | Parts List              | 7-1 |

## INDEX OF ILLUSTRATIONS

Loran Receiving Set AN/SPN-30 (Illustrations of general application to the system) Loran Indicator IP-532/SPN-30 (Cont)

Page

| Figure |                                      | Page  |

|--------|--------------------------------------|-------|

| 4-47.  | Coding in Loran-C System             | 4-56  |

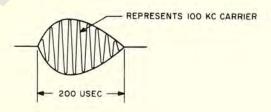

| 4-49.  | Loran-C Pulse, Example of            | 4-57  |

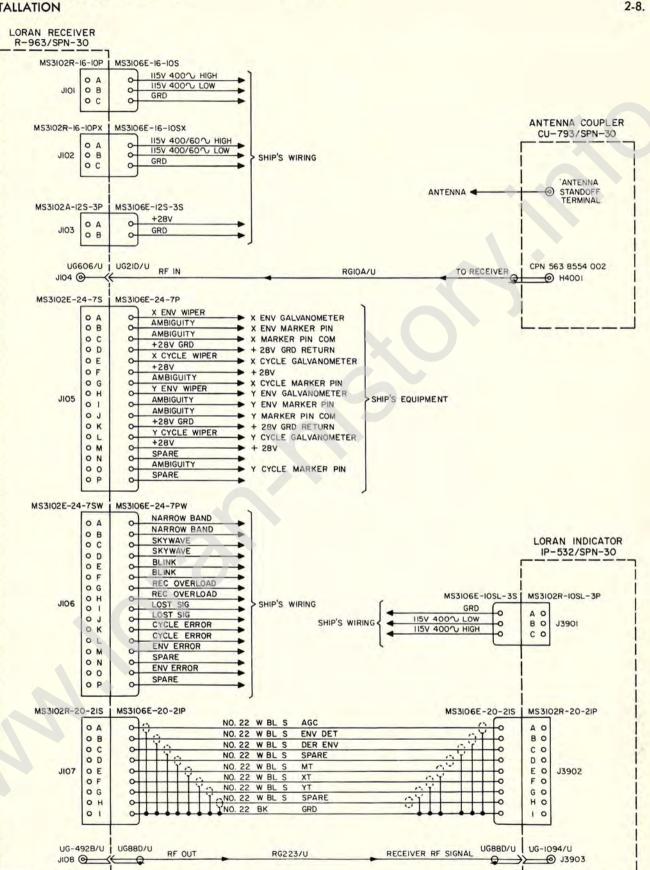

| 2-8.   | Interconnecting Diagram, Loran       |       |

|        | Receiving Set AN/SPN-30              | 2-9   |

| 6-118. | Ohmmeter, Safe, Measuring Circuit .  | 6-116 |

| 6-116. | Ohmmeter, Test Circuit               | 6-115 |

| 6-117. | Ohmmeters, Test, Voltage Versus      |       |

|        | Current Curves for                   | 6-115 |

| 1-2.   | Overall Oblique View                 | 1-1   |

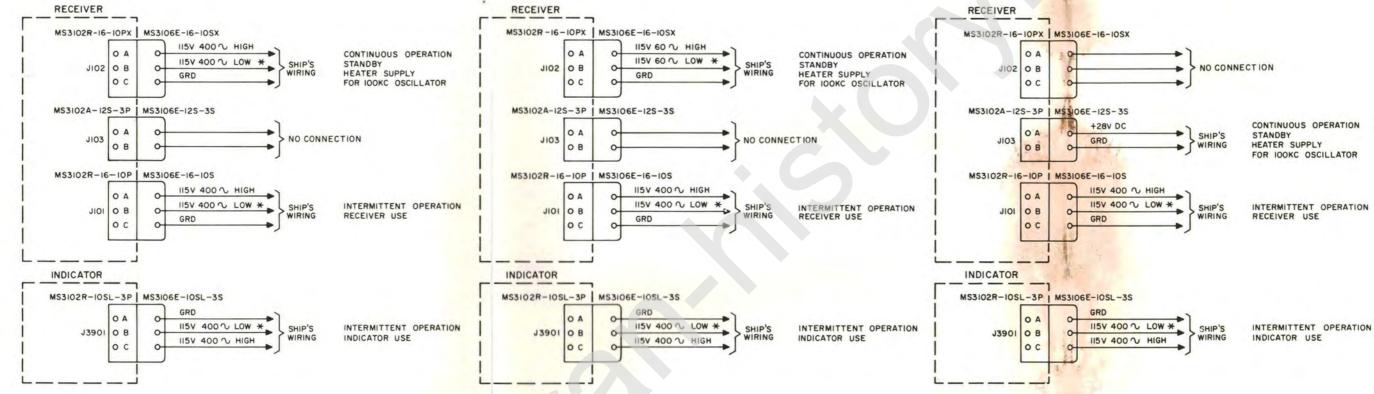

| 2-2.   | Power Supply Connections, Alternate. | 2-2   |

| 4-48.  | Received RF in Loran-C System        | 4-57  |

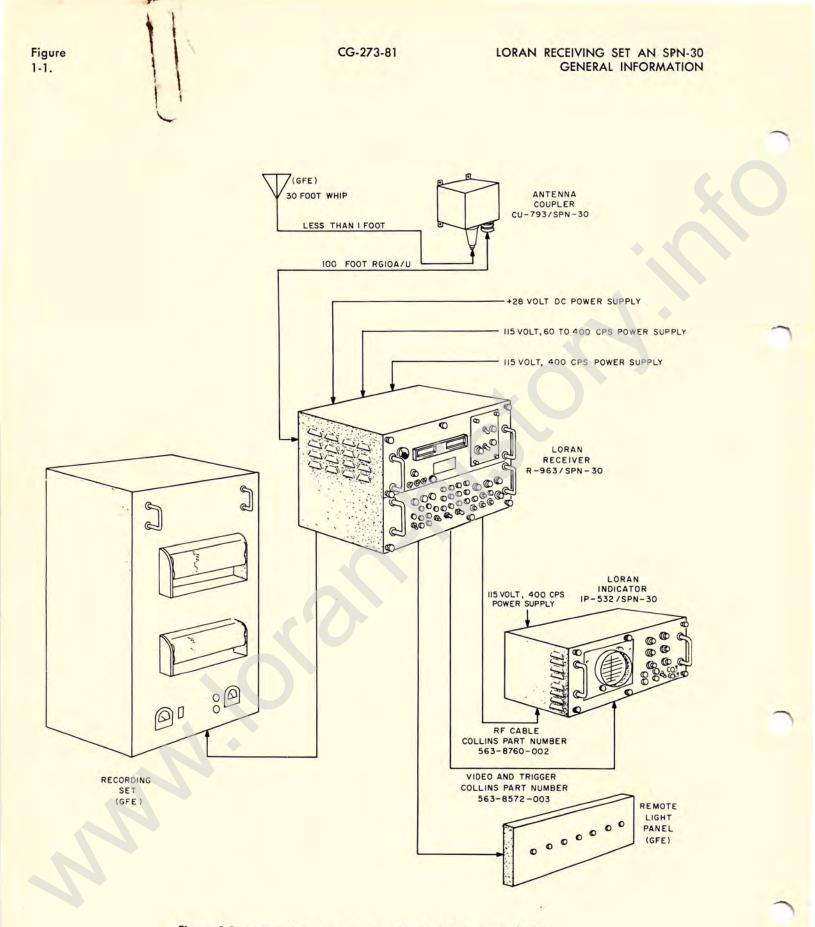

| 1-1.   | Relationship of Units                | 1-0   |

| 6-119. | Terminals, Soldered Printed Circuit  |       |

|        | Board, Removing and Replacing        | 6-116 |

| 6-120. | Terminals, Unsoldered Printed        |       |

|        | Circuit Board, Removing and          |       |

|        | Replacing                            | 6-117 |

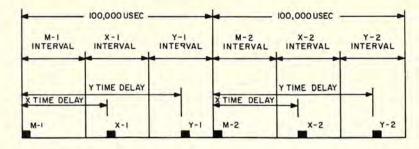

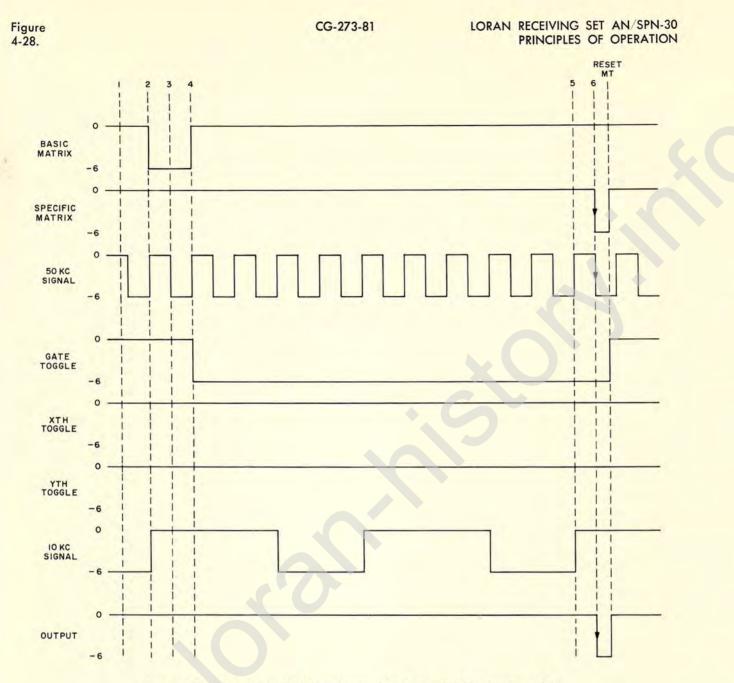

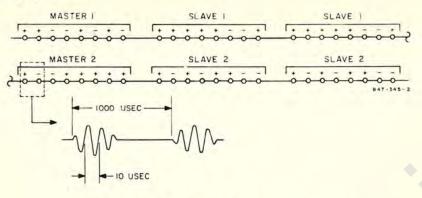

| 4-1.   | Time Sequence Diagram of Pulses      | 1.0   |

|        | from Loran-C Stations                | 4-3   |

| 6-115. | Transistor Circuit, Sample           | 6-114 |

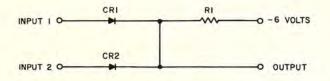

| 4-6.   | Typical AND Circuit, Simplified      | 1.10  |

|        | Schematic Diagram                    | 4-13  |

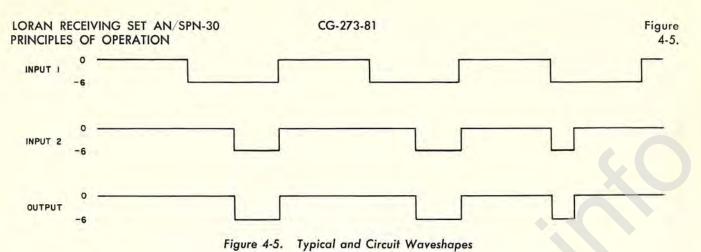

| 4-5.   | Typical AND Circuit Waveshapes       | 4-13  |

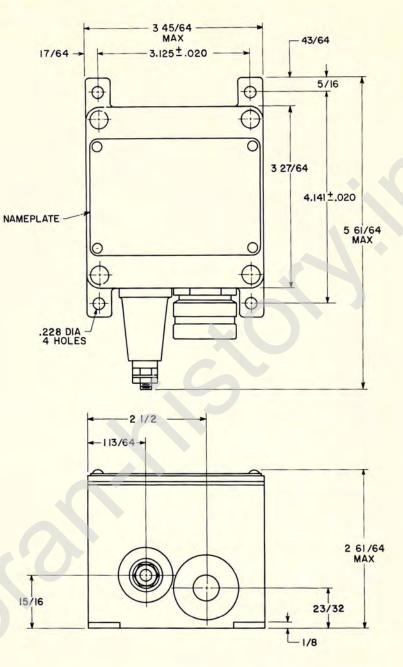

|        | Antenna Coupler CU-793/SPN-30        |       |

| 2-6.   | Outline Drawing                      | 2-7   |

| 5-87.  | Parts Location                       | 5-270 |

| 6-182. | Schematic Diagram                    | 6-253 |

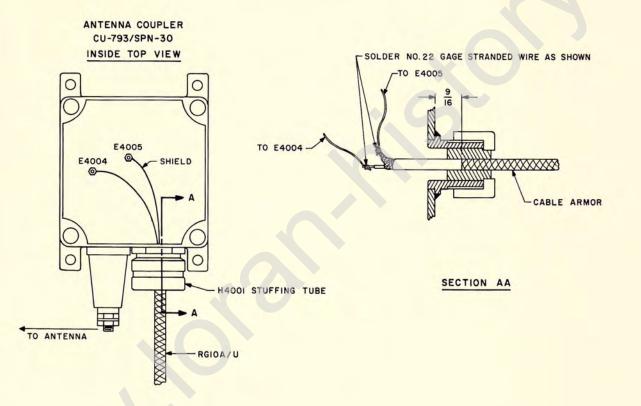

| 2-7.   | Stuffing Tube, Cable Connection to   |       |

|        | Receiver                             | 2-8   |

| 6-114. | Test Setup                           | 6-111 |

|        | Loran Indicator IP-532/SPN-30        |       |

| 6-24.  | Blank Oscillator Output Waveform     | 6-28  |

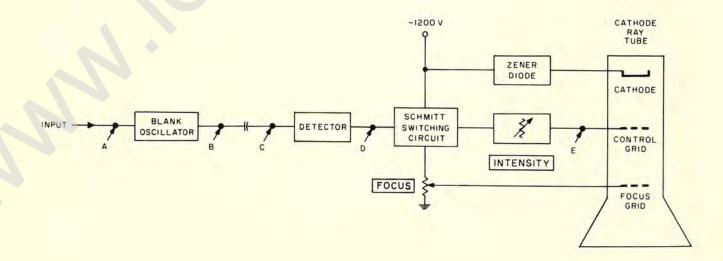

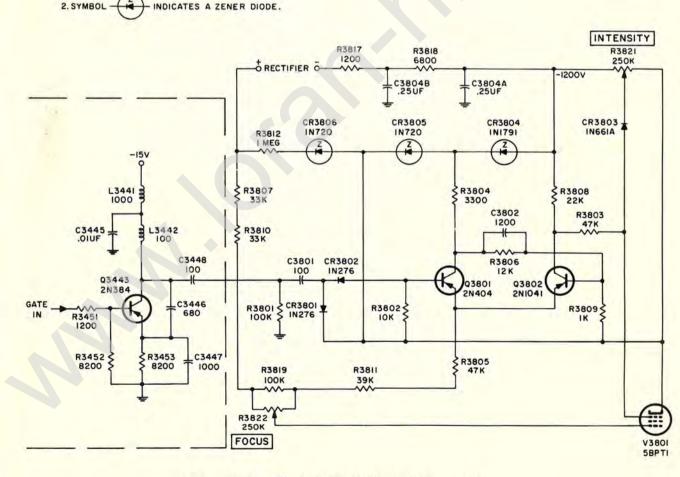

| 4-116. | Blank - Unblank Circuit, Block       | 4.24  |

|        | Diagram                              | 4-123 |

| 4-117. | Blank - Unblank Circuit, Schematic   |       |

|        | Diagram                              | 4-124 |

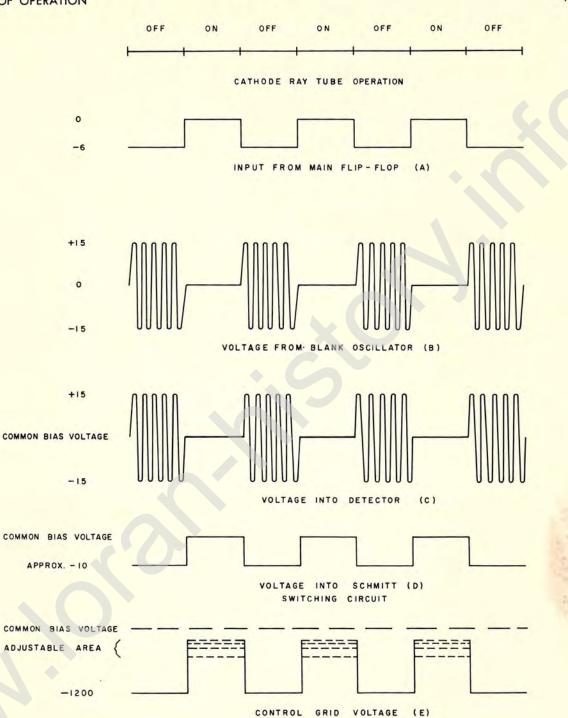

| 4-118. | Blank - Unblank Circuit, Time        |       |

|        | Sequence Diagram                     | 4-125 |

|        |                                      |       |

| Figure          |                                                                        | Page  |

|-----------------|------------------------------------------------------------------------|-------|

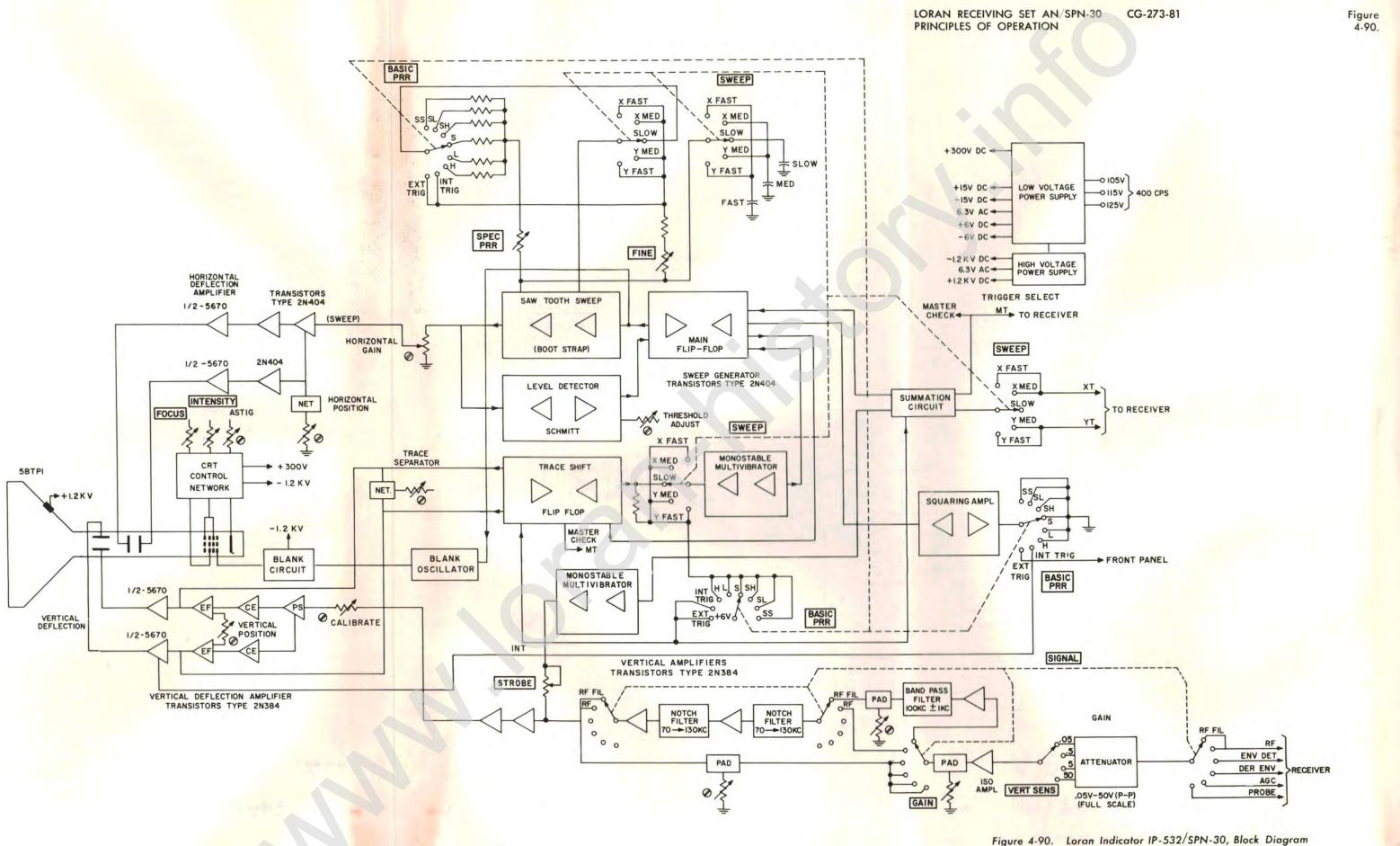

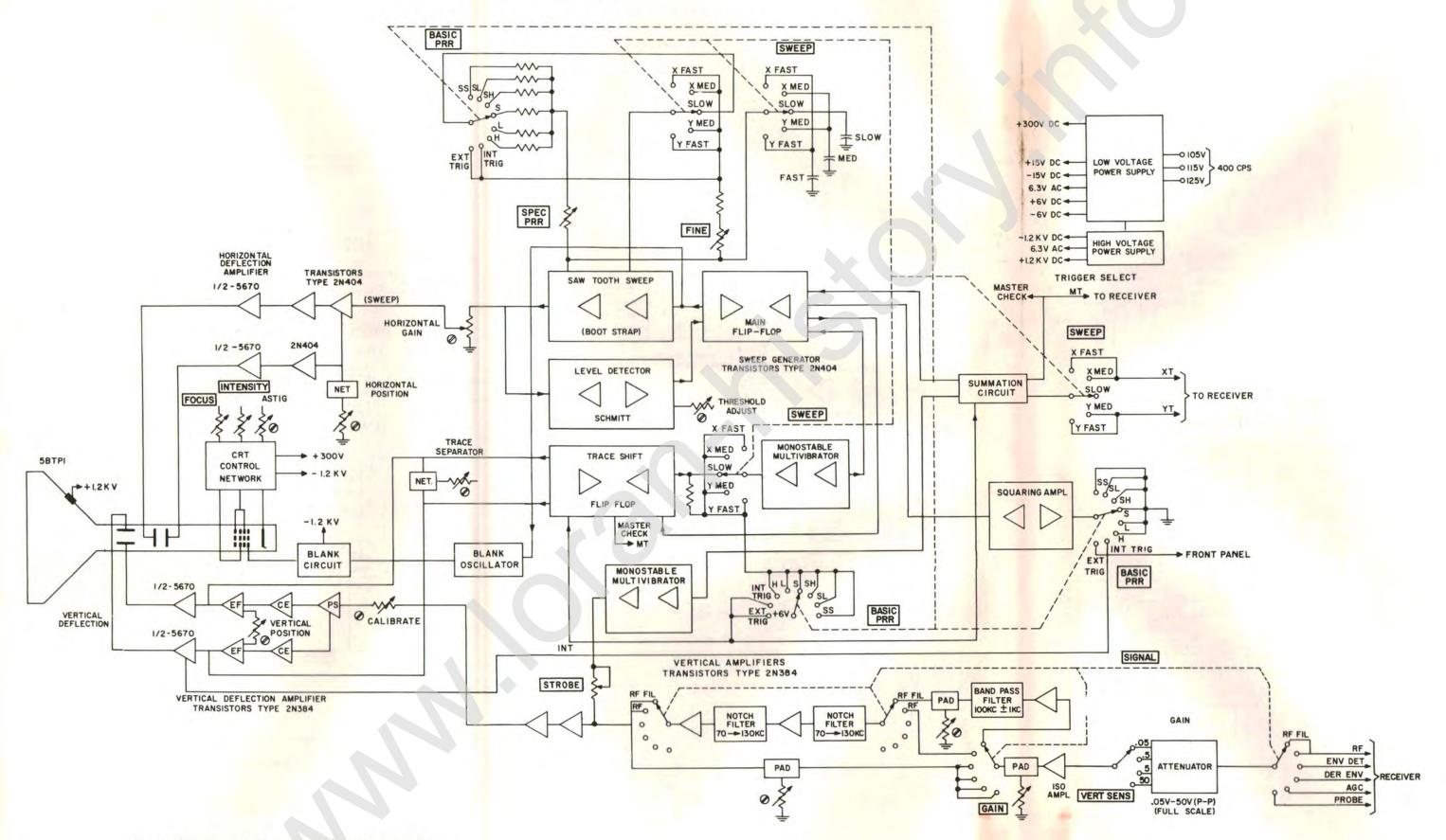

| 6-113.<br>4-90. | Blank - Unblank Test, Waveform for .<br>Block Diagram, Loran Indicator | 6-110 |

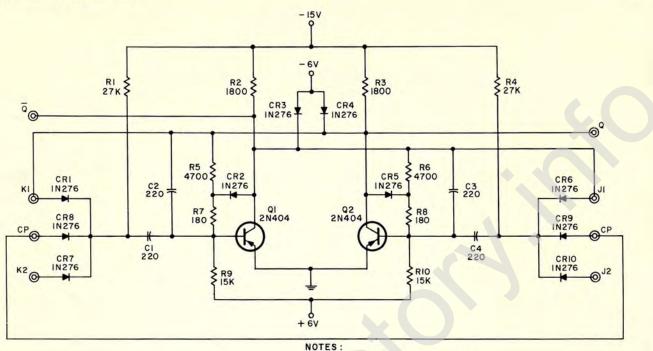

| 4-100.          | IP-532/SPN-30<br>Bootstrap Circuit, Schematic                          | 4-101 |

| 4-99.           | Diagram                                                                | 4-112 |

|                 | Schematic Diagram                                                      | 4-109 |

| 5-86.           | Cabinet Assembly (A3901), Parts<br>Location                            | 5-269 |

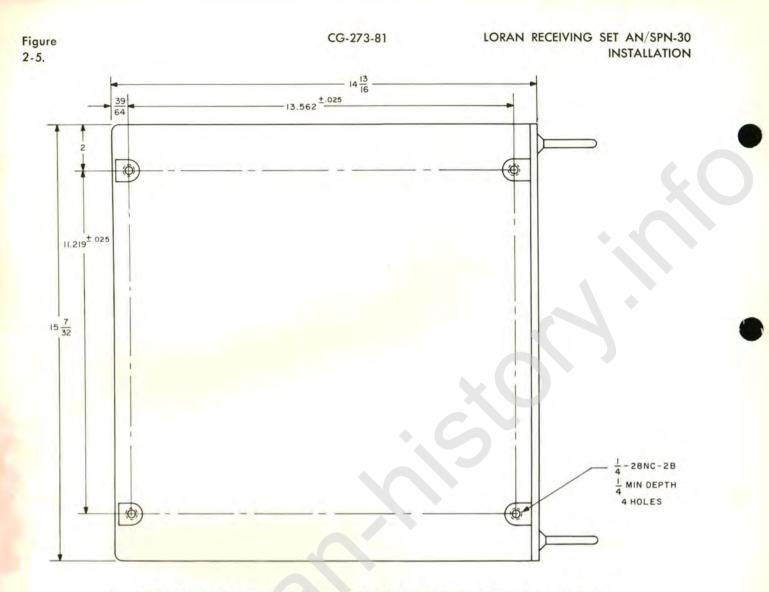

| 2-5.            | Cabinet, Bottom View, Loran<br>Indicator IP-532/SPN-30                 | 2-6   |

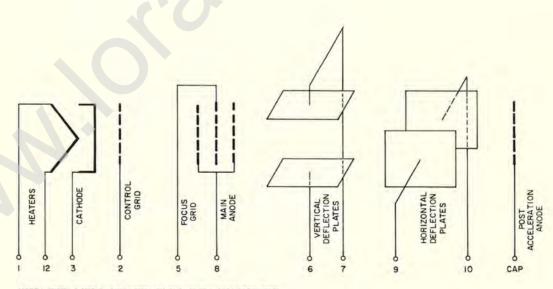

| 4-119.          | Cathode Ray Tube, Tube Elements                                        | 4-126 |

| 5-73.           | Chassis Assembly (A3001), Parts                                        |       |

|                 | Location.                                                              | 5-251 |

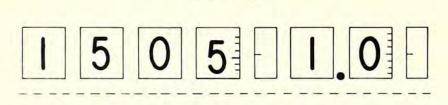

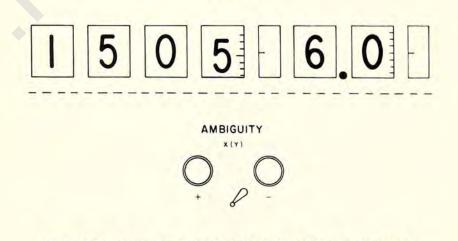

| 3-8.            | Controls and Indicators, Loran                                         | 2.0   |

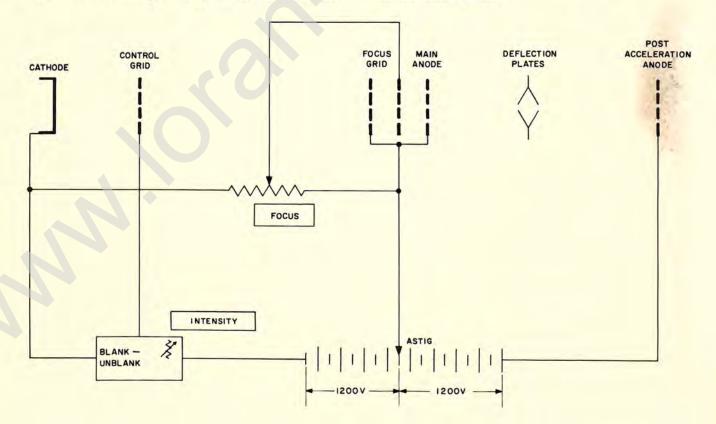

| 4-120.          | Indicator IP-532/SPN-30<br>CRT Control Network, Simplified             | 3-9   |

| 4-120.          | Schematic Diagram                                                      | 4-127 |

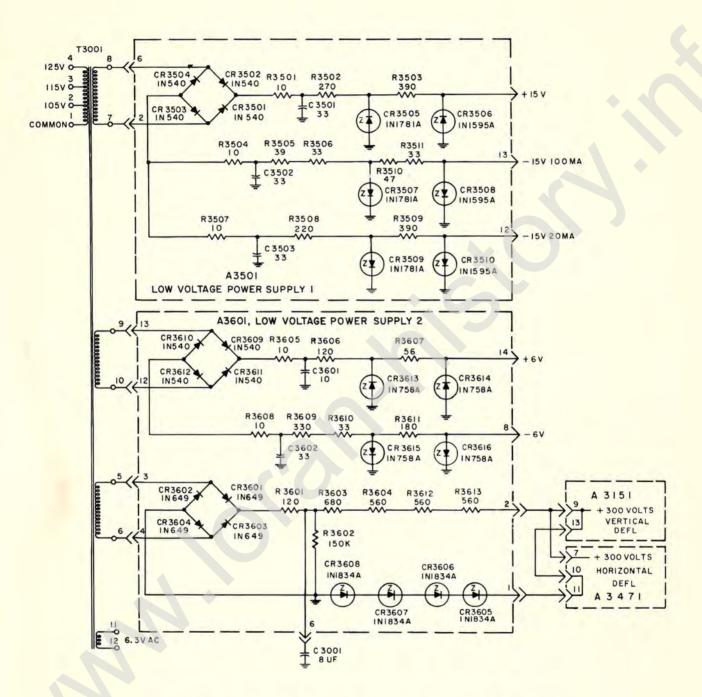

| 5-83.           | 15-Volt Power Supply (A3501), Parts                                    | 1-121 |

| 0-00.           | Location.                                                              | 5-265 |

| 6-110.          | Location                                                               |       |

|                 | Panel for                                                              | 6-108 |

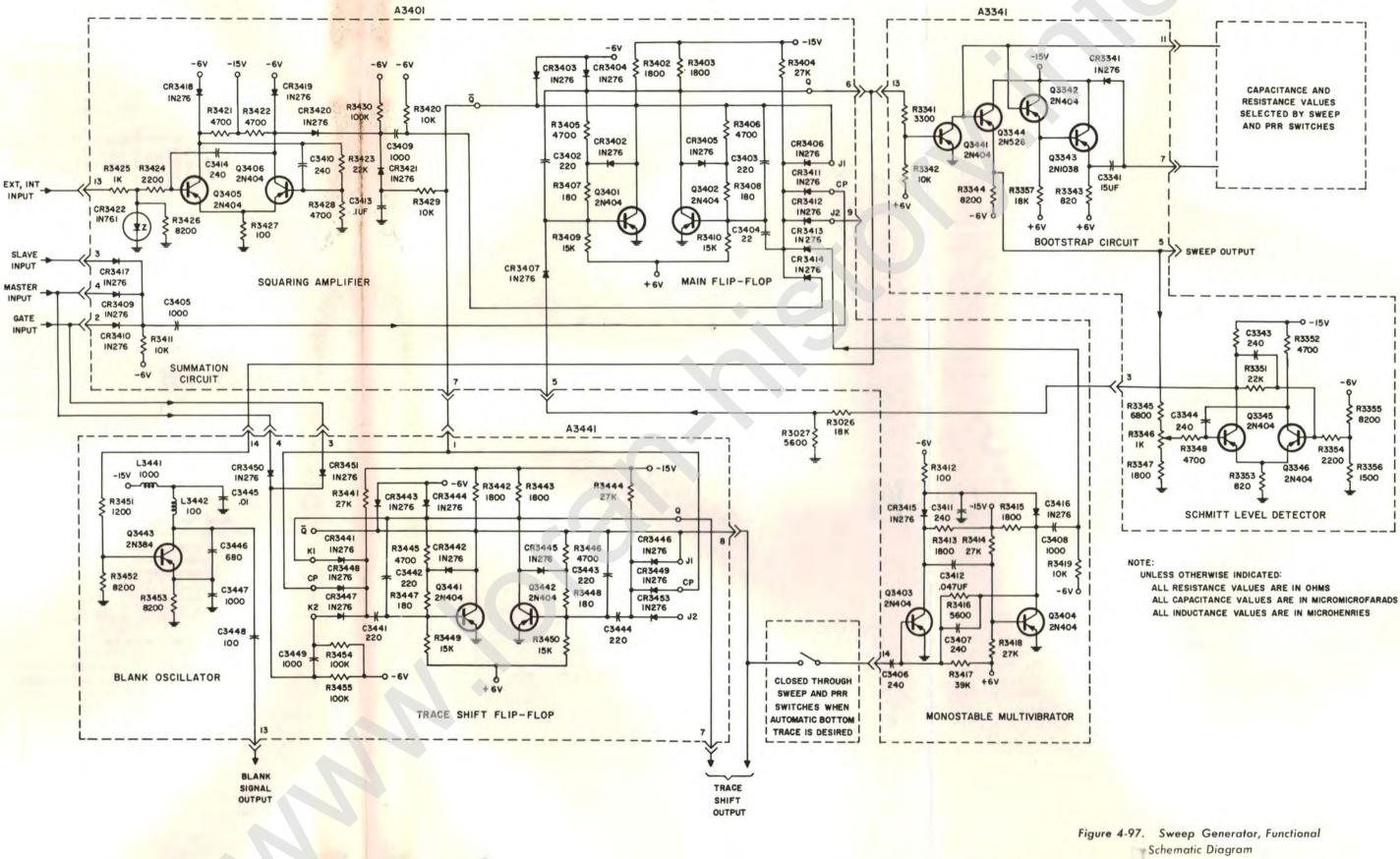

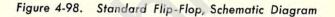

| 4-98.           | Flip-Flop, Standard, Schematic                                         | 5     |

|                 | Diagram                                                                | 4-109 |

| 6-95.           | Flip-Flop Test, Output from Pulse                                      |       |

|                 | Generator to Sweep Generator SA3.                                      | 6-105 |

| 6-104.          | Flip-Flop Test, Pulse Generator                                        | 6 107 |

| E 0E            | Waveform for                                                           | 6-107 |

| 5-85.           | High Voltage - CRT Assembly<br>(A3801), Parts Location                 | 5-267 |

| 6-112.          | High Voltage - CRT Assembly                                            | 0-201 |

| 0-112.          | (A3801), Test Panel for                                                | 6-110 |

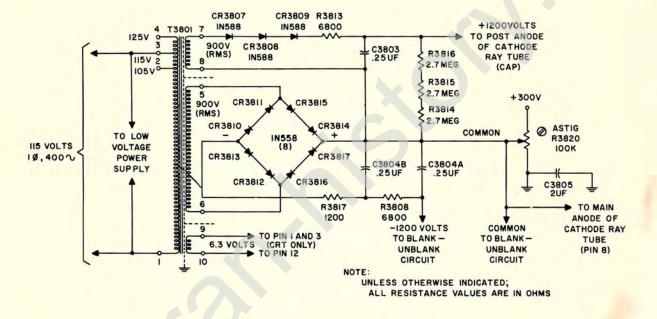

| 4-122.          | High Voltage Power Supply,                                             |       |

|                 | Schematic Diagram                                                      | 4-129 |

| 6-27.           | Horizontal Deflection Amplifier,                                       |       |

|                 | Output Waveforms                                                       | 6-29  |

| 5-82.           | Horizontal Deflection Amplifier                                        |       |

|                 | (A3471), Parts Location                                                | 5-264 |

| 4-109.          | Horizontal Deflection Amplifier,                                       | 1.000 |

|                 | Simplified Schematic Diagram                                           | 4-117 |

| 6-109.          | Horizontal Deflection Amplifier                                        |       |

|                 | (A3471), Test Setup for                                                | 6-107 |

#### ORIGINAL

۷

# INDEX OF ILLUSTRATIONS (Cont)

| Figure          |                                                                      | Page           | Figure          |                                                                         | Page   |

|-----------------|----------------------------------------------------------------------|----------------|-----------------|-------------------------------------------------------------------------|--------|

| 5-19.           | Horizontal Deflection Amplifier<br>(A3471), Voltage and Resistance   |                | 5-78.           | Sweep Generator SA1 (A3301), Parts<br>Location                          | 5-260  |

| 4-113.          | Measurements                                                         | 5-158          | 6-93.           | Sweep Generator SA2 (A3341), Final<br>Adjustment Waveform for           | 6-104  |

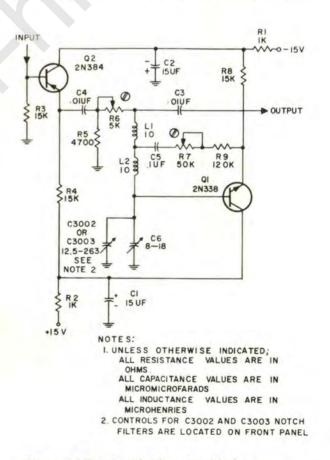

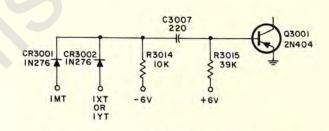

| 4-93.           | Board (E3001)<br>Input Signal Switch                                 | 4-121<br>4-105 | 6-92.           | Sweep Generator SA2 (A3341), Final<br>Test Setup for                    | 6-104  |

| 4-104.          |                                                                      | 4-114          | 5-79.           | Sweep Generator SA2 (A3341), Parts<br>Location                          | 5-261  |

| 6-99.           | Monostable Multivibrator Test,<br>Output for                         | 6-105          | 6-90.           | Sweep Generator SA2 (A3341),<br>Preliminary Test Setup for              | 6-103  |

| 6-98.           | Monostable Multivibrator Test,<br>Output from Pulse Generator to     |                | 6-91.           | Sweep Generator SA2 (A3341),<br>Preliminary Waveforms for               | 6-104  |

| 4-94.           | Sweep Generator SA3                                                  | 6-105<br>4-105 | 4-101.          | Sweep Generator SA2, Schematic<br>Diagram.                              | 4-112  |

| 5-77.           | Notch Filter (A3201, A3202),<br>Parts Location                       | 5-259          | 6-89.           | Sweep Generator SA2 (A3341), Test<br>Jig for.                           | 6-103  |

| 4-112.          | Notch Filter, Simplified Schematic<br>Diagram.                       | 4-120          | 6-96.           | Sweep Generator SA3, Output at<br>Terminals 6 and 7 of A3401            | 6-105  |

| 6-84.           | Notch Filter (A3201, A3202),<br>Test Setup                           | 6-99           | 6-102.          | Sweep Generator SA3, Output for<br>Squaring Amplifier Test              | 6-106  |

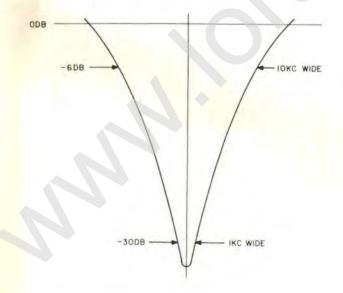

| 4-111.          | Notch Rejection Diagram Oscillator Test, Pulse Generator             | 4-120          | 5-80.           | Sweep Generator SA3 (A3401), Parts<br>Location.                         | 5-262  |

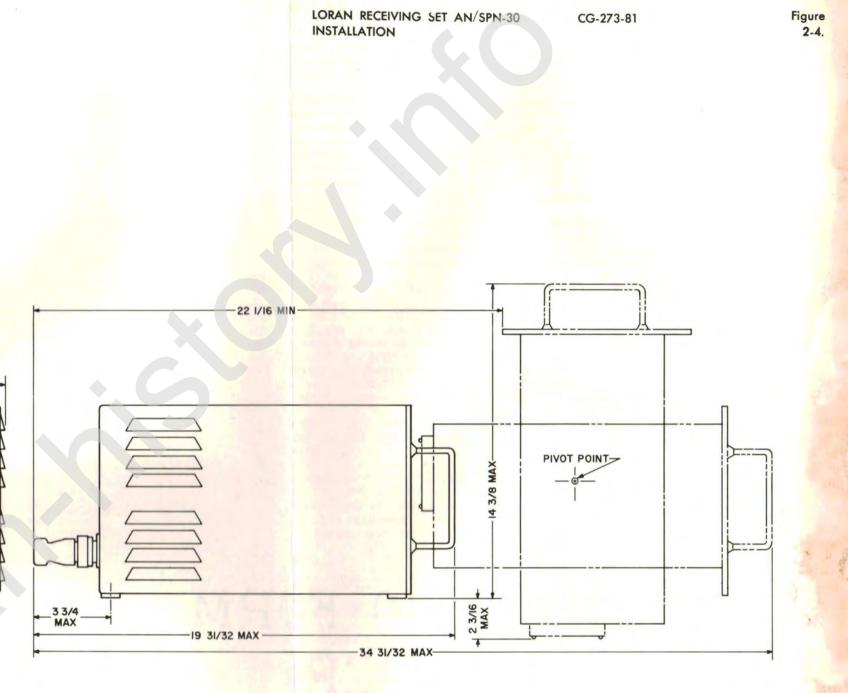

| 2-4.            | Waveform for                                                         | 6-107<br>2-5   | 6-94.           | Sweep Generator SA3 (A3401), Test<br>Setup for Flip-Flop Test.          | 6-105  |

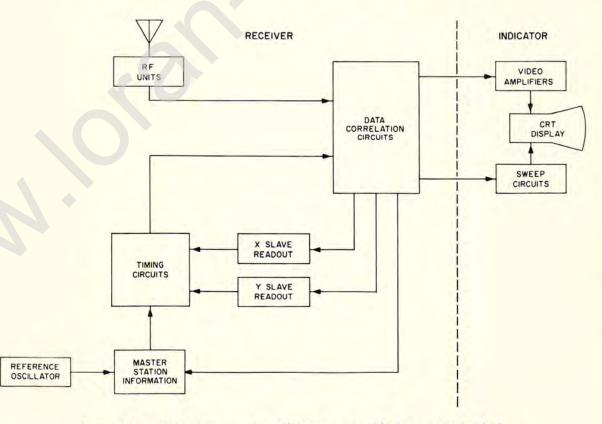

| 4-90.<br>6-183. | Overall Block Diagram                                                | 4-101<br>6-255 | 6-97.           | Sweep Generator SA3 (A3401), Test<br>Setup for Monostable Multivibrator | 0-100  |

| 5-14.           | Power Distribution, Servicing Diagram<br>Probe Adjust Board (E3001), | 5-153          | 6-100           | Test<br>Sweep Generator SA3 (A3401), Test                               | 6-105  |

|                 | Input Circuit<br>Probe Adjust Board (E3001),                         | 4-121          | 0-100.          | Setup for Squaring Amplifier<br>Test                                    | 6-106  |

| 4-92.           | Schematic Diagram<br>Resistance and Capacitance Selecting            | 4-121          | 6-105.          | Sweep Generator SA4 Output for<br>Flip-Flop Test                        | 6-107  |

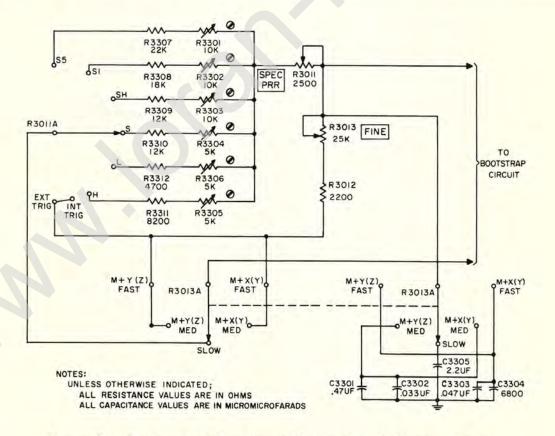

|                 | Network, Bootstrap Circuit<br>Schmitt Level Detector, Schematic      | 4-104          | 6-108.          | Sweep Generator SA4 Output for<br>Oscillator Test                       | 6-107  |

|                 | Diagram                                                              | 4-113          | 5-81.           | Sweep Generator SA4 (A3441), Parts<br>Location.                         | 5-263  |

| 6-23.           | Schematic Diagram<br>Schmitt Level Detector Output                   | 4-112          | 6-106.          | Sweep Generator SA4 (A3441), Test<br>Setup for Oscillator Test          | 6-107  |

| 5-74.           | Waveforms                                                            | 6-28           | 6-103.          | Sweep Generator SA4 (A3441), Test<br>Setup for Flip-Flop Test           | 6-107  |

| 6-85.           | Parts Location<br>Selective Amplifier (A3101), Test                  | 5-256          | 5-3.<br>6-22.   | Test Point Location<br>Test Setup and Applied Waveforms                 | 5-12   |

|                 | Setup                                                                | 6-100          |                 | for Loran Indicator<br>IP-532/SPN-30                                    | 6-27   |

| 5-84.           | Schematic Diagram                                                    | 4-128          | 6-25.<br>4-107. | Trace Shift Waveform                                                    | 6-28   |

|                 | (A3601), Parts Location<br>6- Volt, 300- Volt Power Supply           | 5-266          |                 | Amplifier to Main Flip-Flop,<br>Schematic Diagram                       | 4-115  |

|                 | (A3601), Test Panel for<br>Squaring Amplifier, Schematic             | 6-109          | 6-26.           | Triggering Waveforms with Sweep<br>Control in the Slow Position         | 6-28   |

|                 | Diagram                                                              | 4-116          | 4-119.<br>5-75. |                                                                         | 4-126  |

|                 | from Signal Generator to Sweep<br>Generator SA3                      | 6-106          | 6-86.           | Location                                                                | 5-257  |

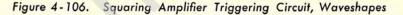

| 4-105.          | Squaring Amplifier Triggering<br>Circuit, Block Diagram              | 4-115          | 6-88.           | Setup<br>Vertical Deflection Amplifier                                  | 6-101  |

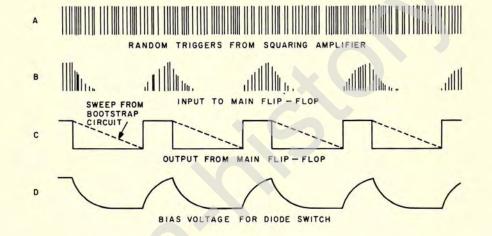

| 4-106.          | Squaring Amplifier Triggering<br>Circuit, Waveshapes                 | 4-115          | 5-76.           | (A3151), Output Measuring of<br>Vertical Deflection Amplifier           | 6-102  |

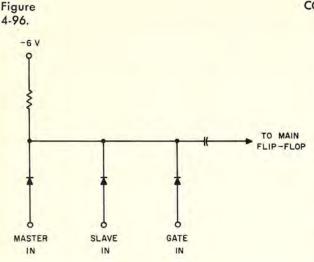

| 4-96.           | Summation Circuit, Simplified<br>Schematic Diagram                   | 4-106          |                 | (A3151), Parts Location<br>Vertical Deflection Amplifier,               | 5-258  |

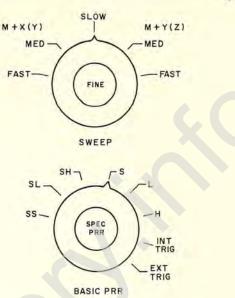

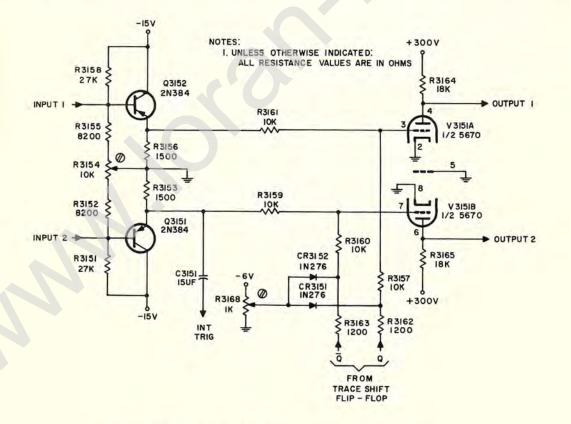

| 4-91.<br>4-97.  | Sweep Controls                                                       | 4-103          | 6-87.           | Schematic Diagram<br>Vertical Deflection Amplifier                      | 4-122  |

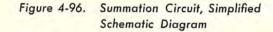

| vi              | Schematic Diagram                                                    | 4-107          |                 | (A3151), Test Setup                                                     | 6-101  |

|                 |                                                                      |                |                 |                                                                         | IN TAL |

# INDEX OF ILLUSTRATIONS (Cont)

| Figure         |                                                                            | Page         |

|----------------|----------------------------------------------------------------------------|--------------|

| 5-18.          | Vertical Deflection Amplifier                                              |              |

| 4-110.         | (A3151), Voltage and Resistance<br>Measurements                            | 5-158        |

| 4-110.         | Diagram.                                                                   | 4-119        |

| 4-95.          | Vertical Sensitivity Switch.                                               | 4-119        |

| 1-00.          |                                                                            | 1-100        |

|                | Loran Receiver R-963/SPN-30                                                |              |

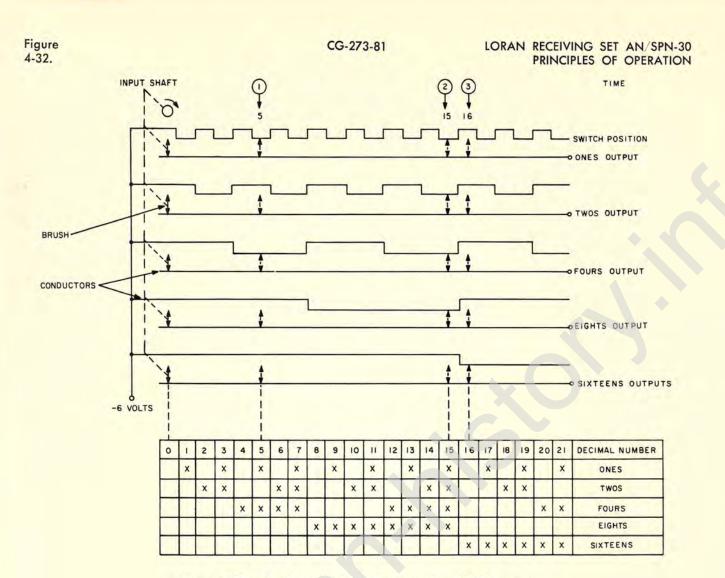

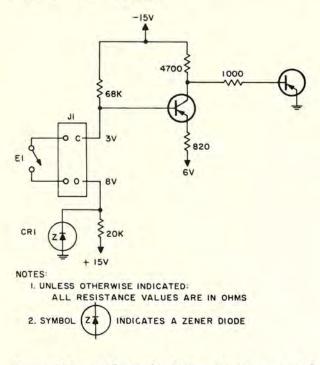

| 4-33.          | ADC-Encoder Driver, Interconnection<br>of Drive Bias, Simplified Schematic |              |

|                | Diagram                                                                    | 4-41         |

| 6-36.          | AGC Curve, Typical                                                         | 6-41         |

| 5-52.          | AGC Driver (A1504), Parts<br>Location                                      | 5-223        |

| 6-152.         | AGC Driver (A1504), Schematic                                              |              |

|                | Diagram                                                                    | 6-193        |

| 6-64.          | AGC Driver (A1504), Test Setup                                             | 6-71         |

| 5-54.          | AGC Gate (A1506), Parts Location                                           | 5-225        |

| 6-154.         | AGC Gate (A1506), Schematic                                                |              |

|                | Diagram.                                                                   | 6-197        |

| 6-66.          | AGC Gate (A1506), Test Setup                                               | 6-73         |

| 5-55.          | AGC Integrator (A1507 - A1509),                                            | F 000        |

| C 155          | Parts Location                                                             | 5-226        |

| 6-155.         | AGC Integrator (A1507 - A1509),                                            | 6 100        |

| 6-67.          | Schematic Diagram<br>AGC Integrator (A1507 - A1509),                       | 6-199        |

| 0-07.          | Test Setup                                                                 | 6-74         |

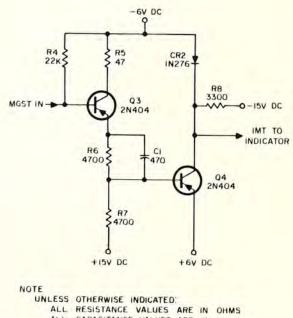

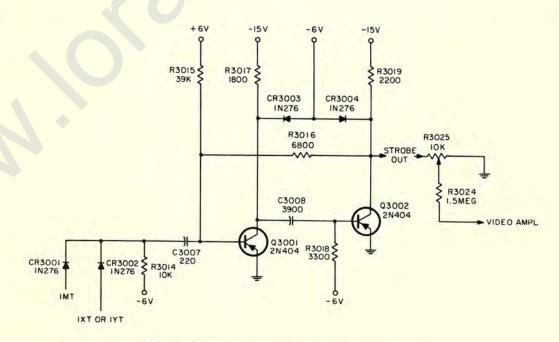

| 4-78.          | AGC Monitor IMT Circuit, Simplified                                        | 0-13         |

| 1 10.          | Schematic Diagram                                                          | 4-77         |

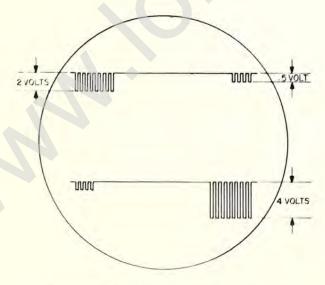

| 4-77.          | AGC Monitor Output, Sample Scope                                           |              |

|                | Display                                                                    | 4-77         |

| 5-56.          | AGC Monitor (A1510), Parts                                                 |              |

|                | Location                                                                   | 5-267        |

| 6-156.         | AGC Monitor (A1510), Schematic                                             | 0.0200       |

|                | Diagram.                                                                   | 6-201        |

| 6-68.          | AGC Monitor (A1510), Test Setup                                            | 6-74         |

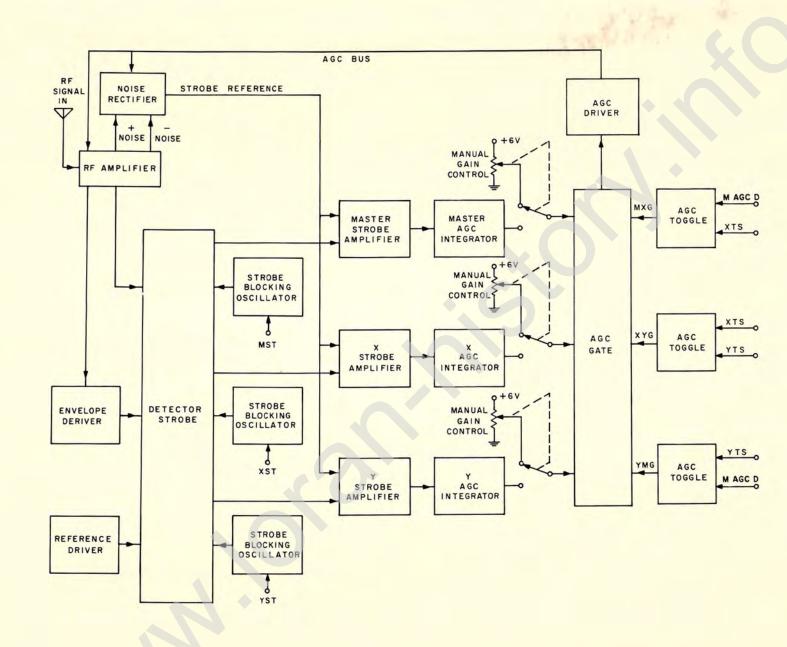

| 4-74.<br>6-21. | AGC Time Sequence Diagram Ambiguity Cam Orientation                        | 4-73<br>6-25 |

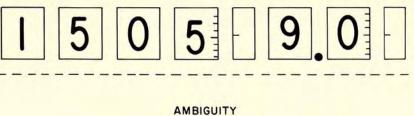

| 3-3.           | Ambiguity Indication, Example 1A,                                          | 0-20         |

| 0-0.           | Loran Receiver R-963/SPN-30                                                | 3-6          |

| 3-4.           | Ambiguity Indication, Example 1B,                                          |              |

|                | Loran Receiver R-963/SPN-30                                                | 3-6          |

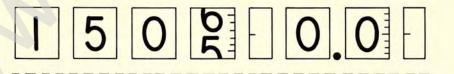

| 3-5.           | Ambiguity Indication, Example 2,                                           |              |

|                | Loran Receiver R-963/SPN-30                                                | 3-6          |

| 3-6.           | Ambiguity Indication, Example 3A,                                          |              |

|                | Loran Receiver R-963/SPN-30                                                | 3-7          |

| 3-7.           | Ambiguity Indication, Example 3B,                                          | 0.7          |

| 0 100          | Loran Receiver R-963/SPN-30                                                | 3-7          |

| 6-173.         | Analog-to-Digital Converter,                                               | 6-235        |

| 4-32.          | Schematic Diagram<br>Analog-to-Digital Converter,                          | 0-230        |

| 2-04.          | Simplified Diagram                                                         | 4-40         |

| 5-9.           | Analog-to-Digital Converter,                                               |              |

|                | Servicing Diagram, Loran Receiver                                          |              |

|                | R-963/SPN-30                                                               | 5-143        |

| 6-175.         |                                                                            |              |

|                | Diagram                                                                    | 6-239        |

| 6-178.         | Assembly Board (E1004), Schematic                                          | Sec. 1       |

|                | Diagram                                                                    | 6-245        |

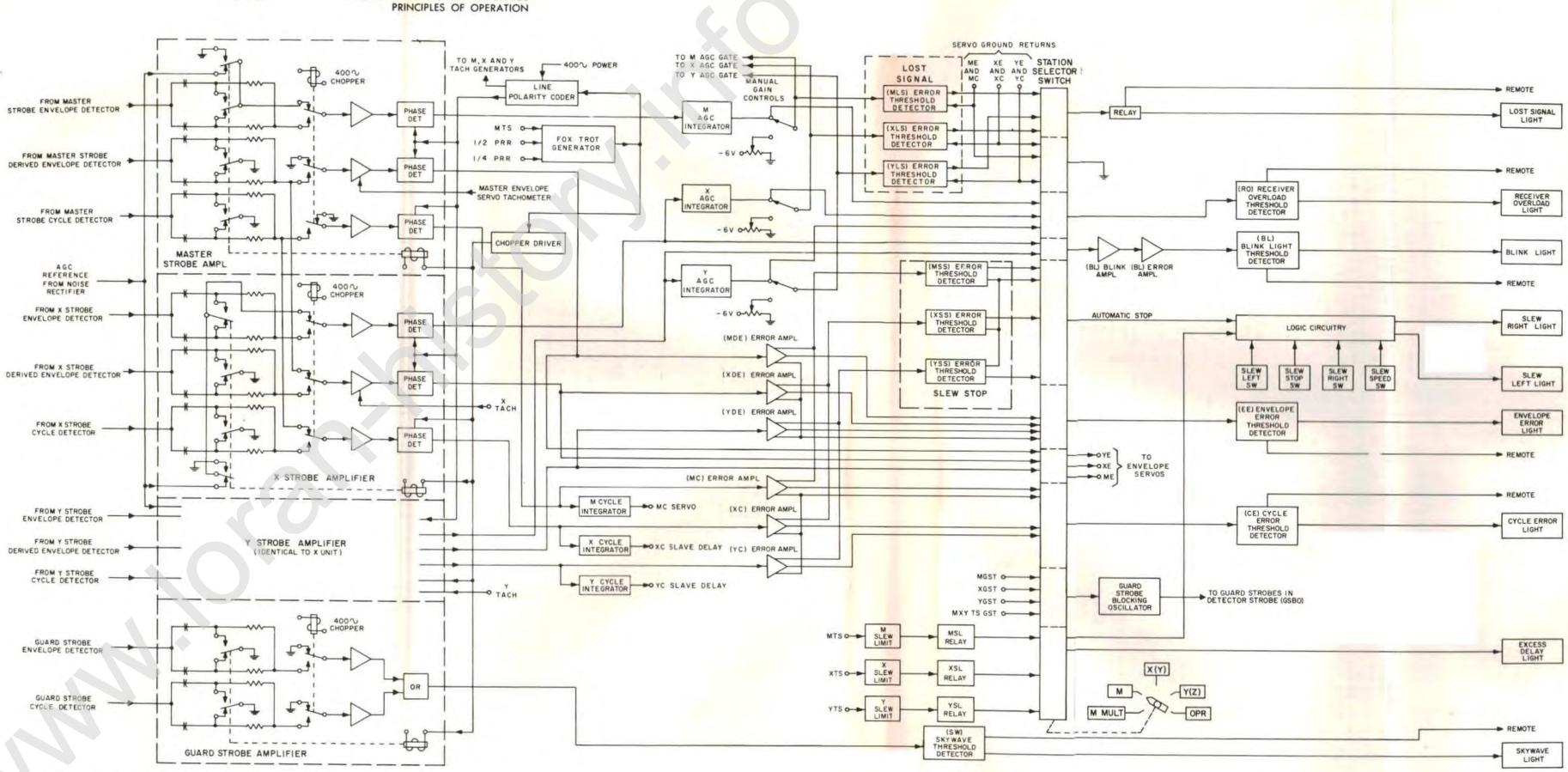

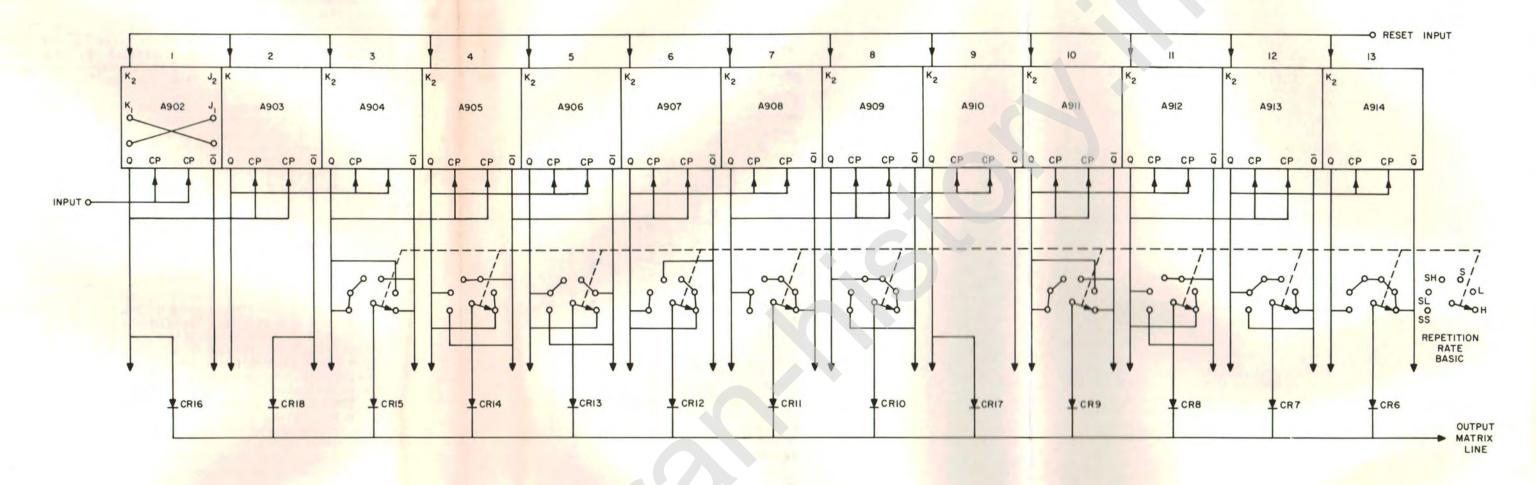

| 4-26.          | Basic Counter and Basic Repetition                                         |              |

|                | Rate Switch.                                                               | 4-33         |

| 6-176.         |                                                                            | 6 044        |

|                | Schematic Diagram                                                          | 6-241        |

| ORIGIN         | IAL                                                                        |              |

|                |                                                                            |              |

| Figure         |                                                                             | Page      |

|----------------|-----------------------------------------------------------------------------|-----------|

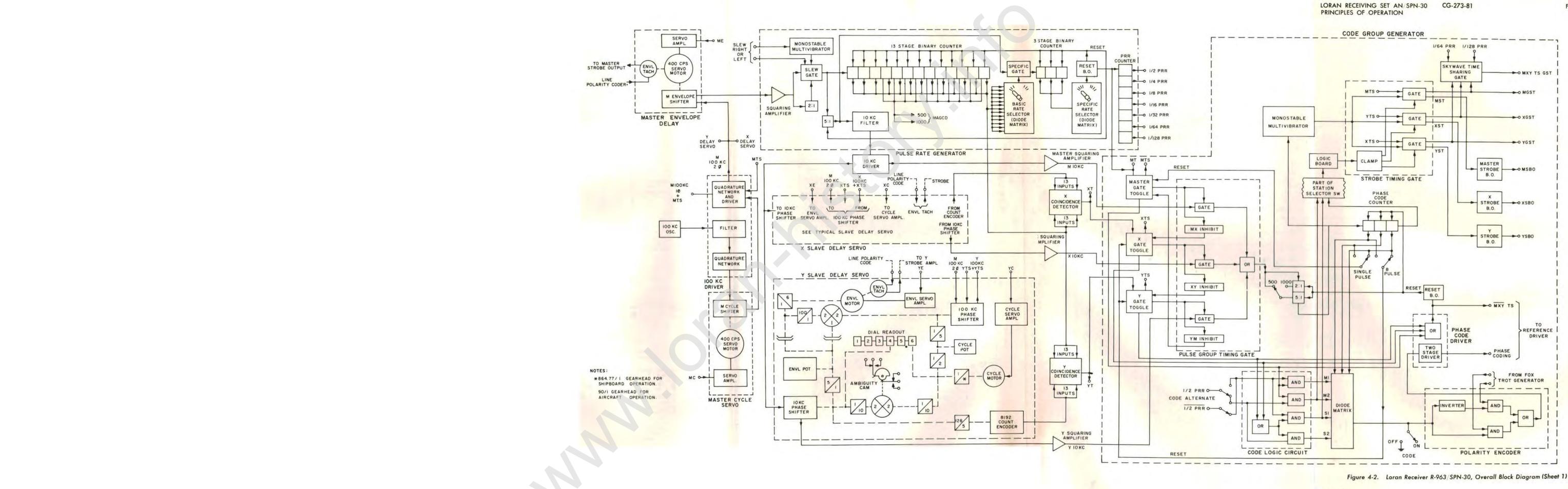

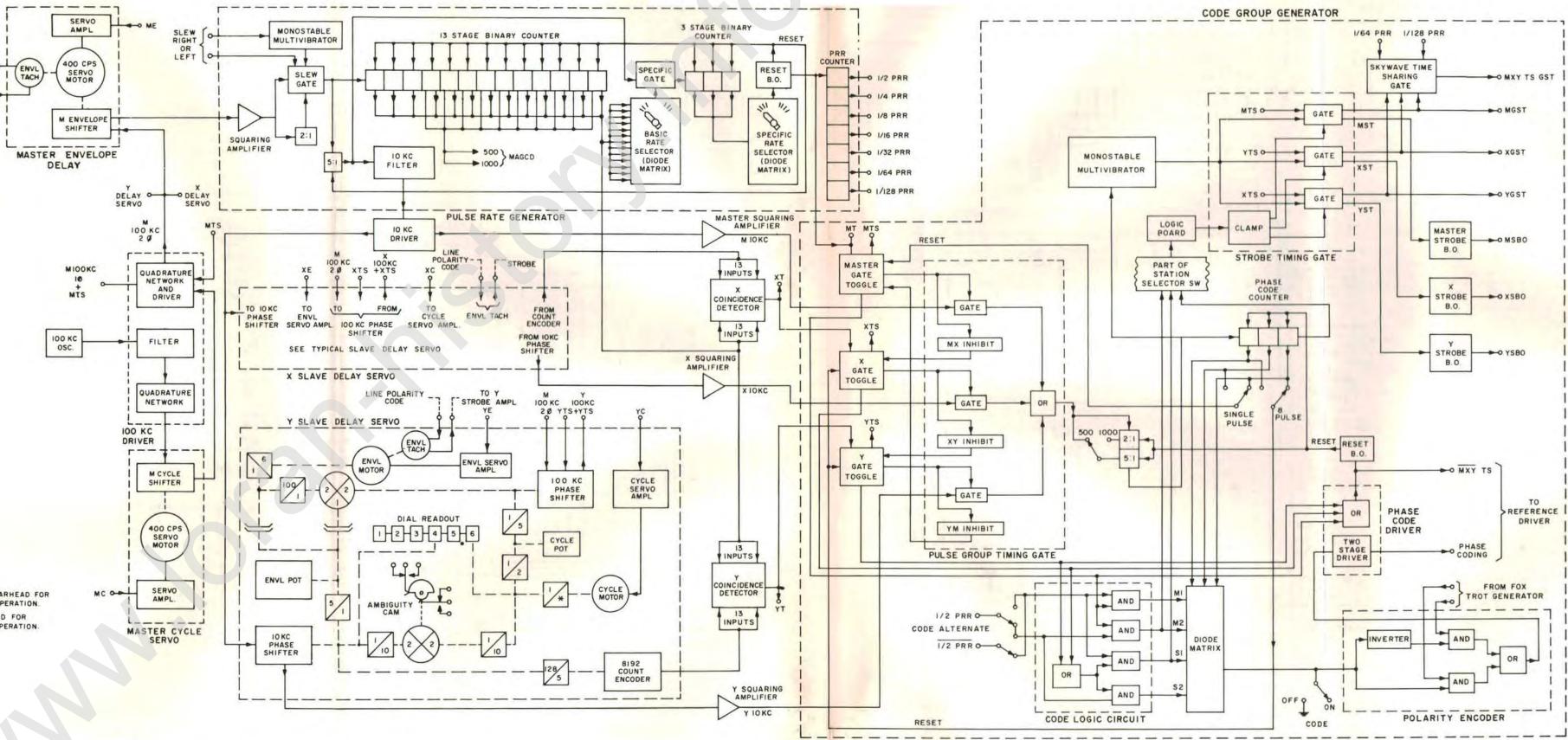

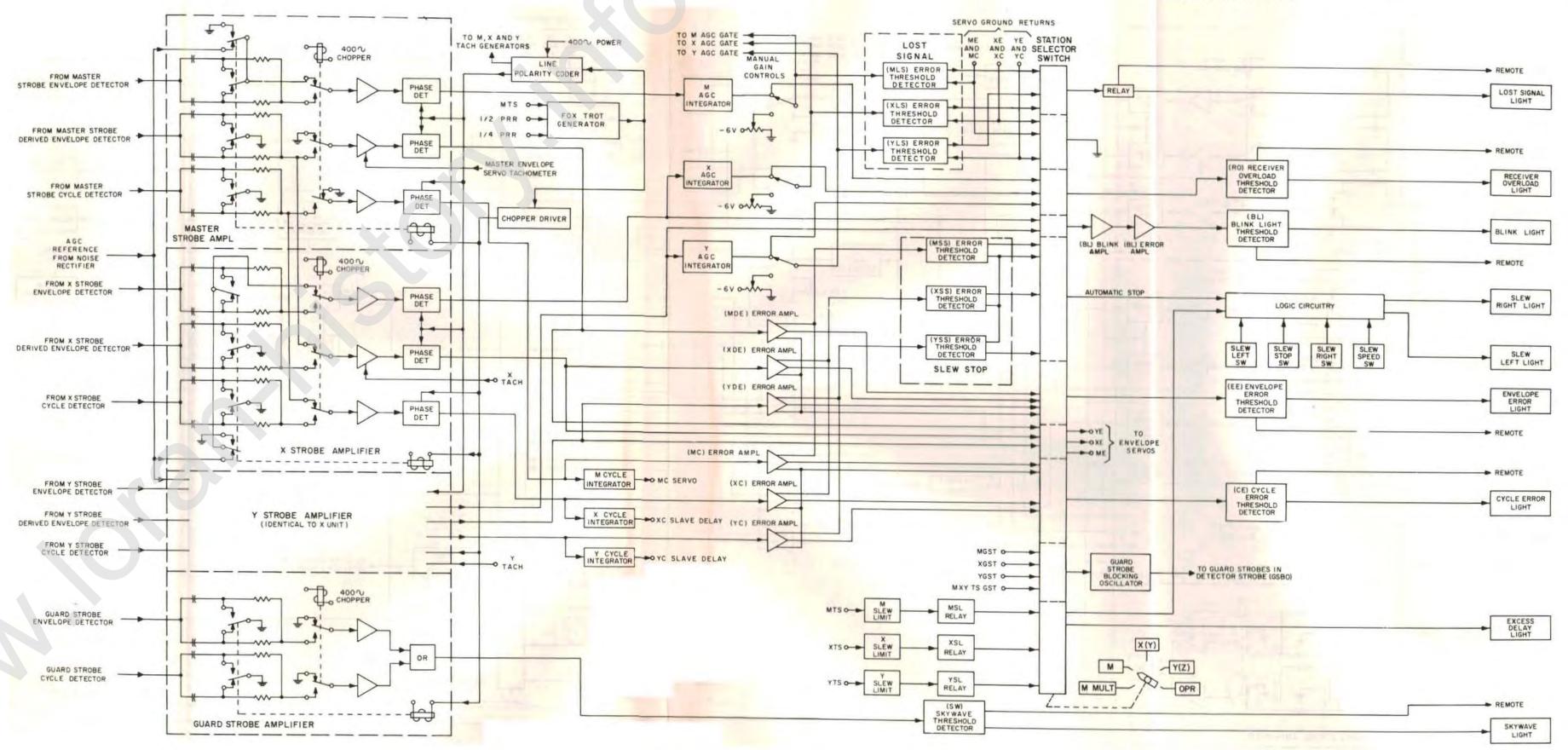

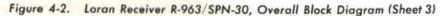

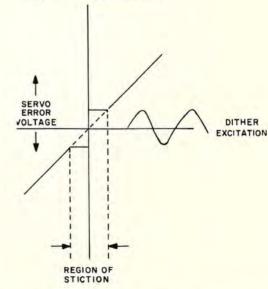

| 4-2.           | Block Diagram, Overall, Loran<br>Receiver R-963/SPN-30                      | 4-5       |

| 3-1.           | Block Diagram, Simplified, Loran<br>Receiver R-963/SPN-30                   | 3-1       |

| 5-60.          | Blink Light Amplifier (A1621),<br>Parts Location                            | 5-231     |

| 6-160.         | Blink Light Amplifier (A1621),<br>Schematic Diagram                         | 6-209     |

| 6-71.          | Blink Light Amplifier (A1621),<br>Test Setup                                | 6-78      |

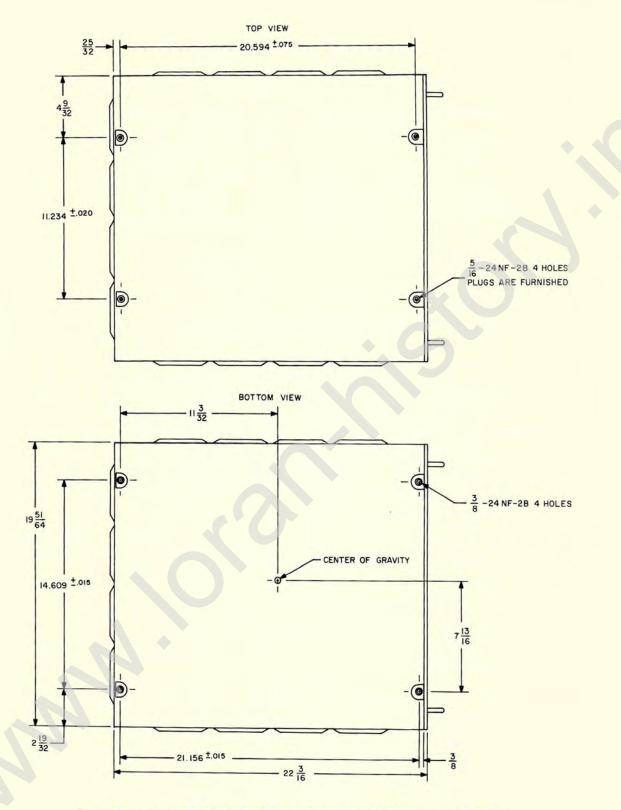

| 2-1.           | Cabinet, Top & Bottom View, Loran<br>Receiver R-963/SPN-30                  | 2-0       |

| 5-36.          | Chassis Assembly (A1001), Parts<br>Location                                 | 5-187     |

| 5-71.          | Chopper Driver (A2702), Parts<br>Location                                   | 5-249     |

| 6-171.         | Chopper Driver (A2702), Schematic<br>Diagram.                               | 6-231     |

| 6-82.          | Chopper Driver (A2702), Test Setup .                                        | 6-97      |

| 6-16.          | Chopper Driver, Waveform at A2702, TP2.                                     | 6-19      |

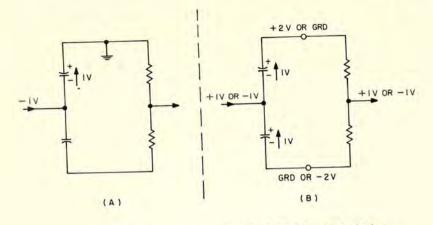

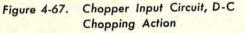

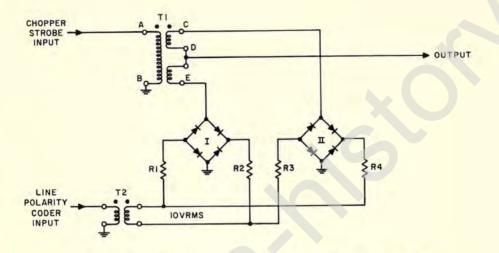

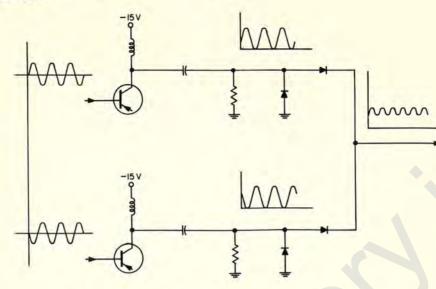

| 4-66.          | Chopper Input Circuit, A-C Chopping<br>Action                               | 4-68      |

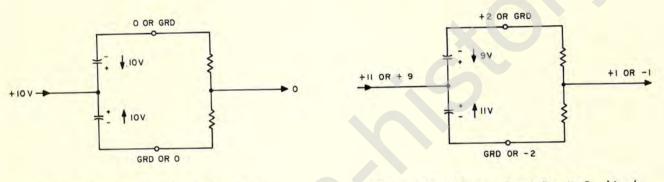

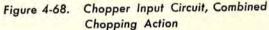

| 4-68.          | Chopper Input Circuit, Combined<br>Chopping Action.                         | 4-68      |

| 4-67.          | Chopper Input Circuit, D-C Chopping                                         | 4-68      |

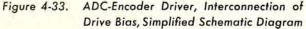

| 4-34.          | Action                                                                      | 4-44      |

| 5-11.          | Code Group Generator, Servicing Dia-<br>gram, Loran Receiver R- 963/SPN- 30 | 5-147     |

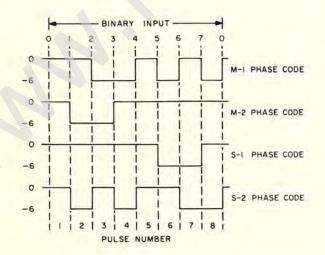

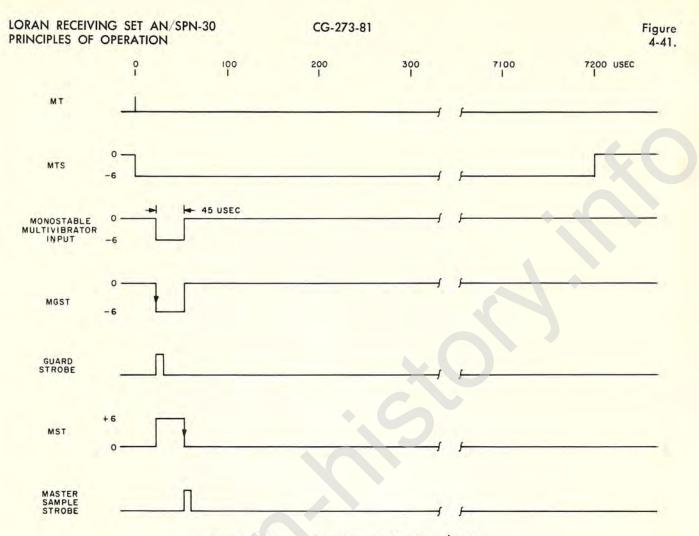

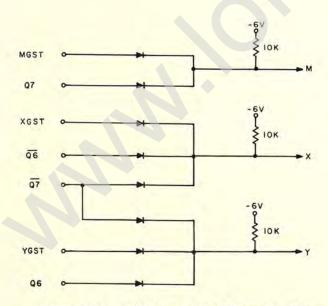

| 4-38.          | Code Logic Circuit, Waveshapes<br>and Time Relationship Diagram             | 4-48      |

| 5-41.          | Code Logic (A1315), Parts Location .                                        | 5-208     |

| 6-141.         | Code Logic (A1315), Schematic<br>Diagram.                                   | 6-171     |

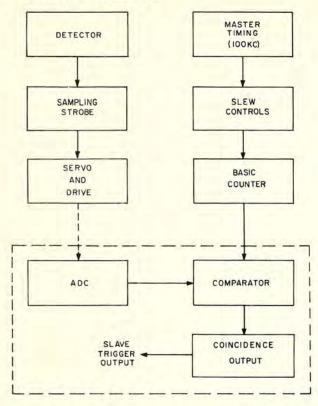

| 4-31.          | Coincidence Detector, Simplified<br>Block Diagram                           | 4-39      |

| 5-38.          | Coincidence Output (A1214), Parts                                           | 5-205     |

| 6-138.         | Location                                                                    | 6-165     |

| 5-37.          | Comparator (A1201 - A1213),                                                 |           |

| 6-137.         |                                                                             | 5-204     |

| 6- 53.         | Schematic Diagram<br>Comparators (A1201 - A1213),                           | 6-163     |

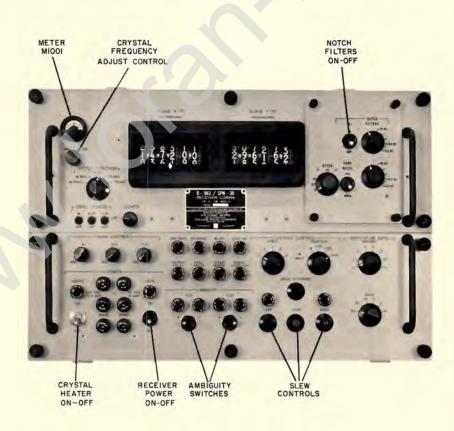

| 3-2.           | Test Setup for<br>Controls and Indicators, Loran                            | 6-57      |

|                | Receiver R-963/SPN-30                                                       | 3-2       |

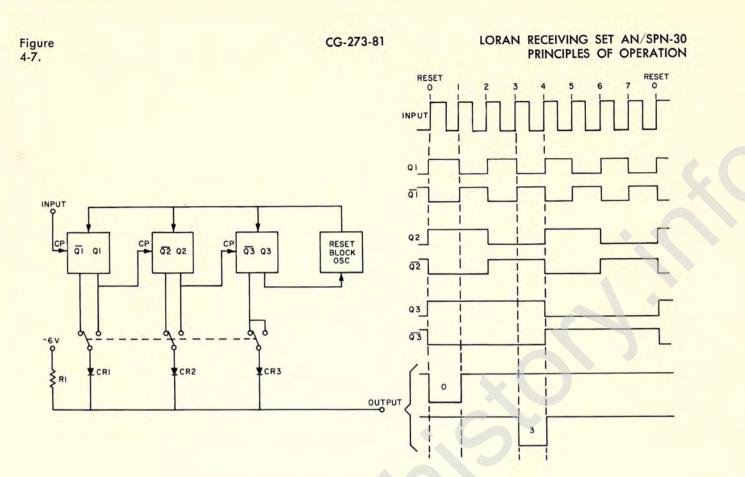

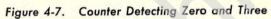

| 4-7.<br>6-14.  | Counter Detecting Zero and Three                                            | 4-14 6-18 |

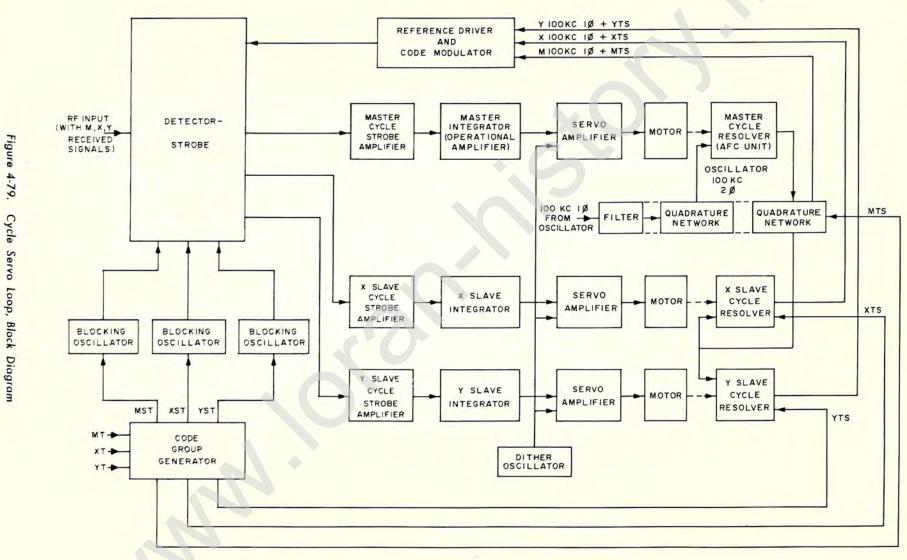

| 6-14.<br>4-79. | CW Signal Injection, Test Setup Cycle Servo Loop, Block Diagram             | 4-79      |

| 5-68.          | Cycle Time Constant Module                                                  |           |

| 6-168.         |                                                                             | 5-246     |

| 6-80.          | Schematic Diagram<br>Cycle Time Constant (A2501), Test                      | 6-225     |

| 1 00           | Setup.                                                                      | 6-95      |

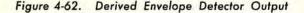

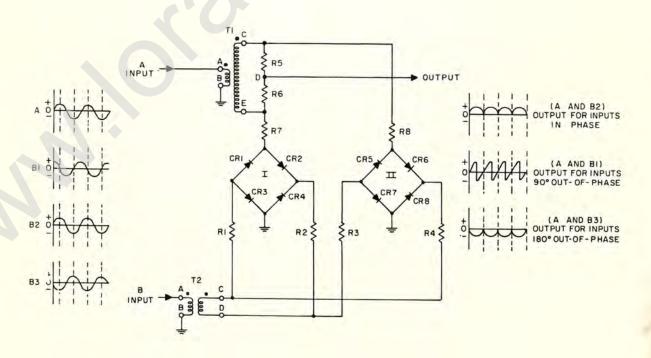

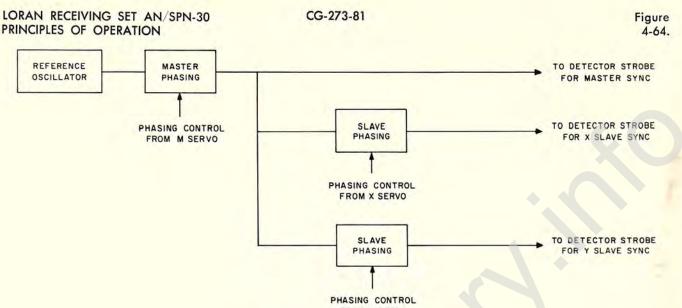

| 4-62.<br>4-63. | Derived Envelope Detector Output<br>Detector Contained in Detector-         | 4-65      |

|                | Strobe Unit, Example Schematic<br>Diagram                                   | 4-65      |

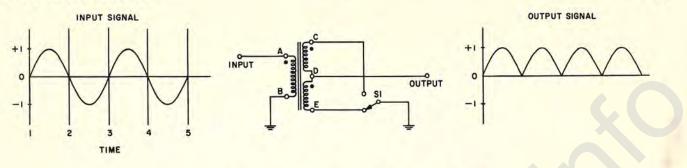

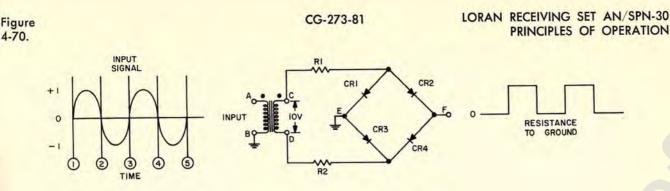

| 4-70.          | Detector Diode Switching                                                    | 4-70      |

|                |                                                                             | vii       |

.

Page

6-76

5-228

6-203

6-75

4 - 23

6-249

6-9 4-14

4-62

5-215

6-185

6-64

4-63

4-63

4-63

6-37

6-19 4-72

4-75

4-88

4-64

5-173

6-141

6-46

4-71

5-242

6-221

6-94

4-38

2-9

6-3

6-19

5-248

6-229

6-96

6-50

ORIGINAL

### **INDEX OF ILLUSTRATIONS (Cont)**

| Figure         |                                                                            | Page           | Figure         |                                                                   |   |

|----------------|----------------------------------------------------------------------------|----------------|----------------|-------------------------------------------------------------------|---|

| 5-23.          | Detector-Strobe Module (A401),<br>Parts Location                           | 5-167          | 6-70.          | Error Amplifier (A1613 - A1619),<br>Test Setup                    |   |

| 6-124.         | Detector-Strobe Module (A401),<br>Schematic Diagram                        | 6-137          | 5-57.          | Error Threshold Detector (A1601 -<br>A1610), Parts Location       | - |

| 6-38.          | Detector-Strobe Module (A401),<br>Test Setup                               | 6-43           | 6-157.         | Error Threshold Detector (A1601 -<br>A1610), Schematic Diagram    | ( |

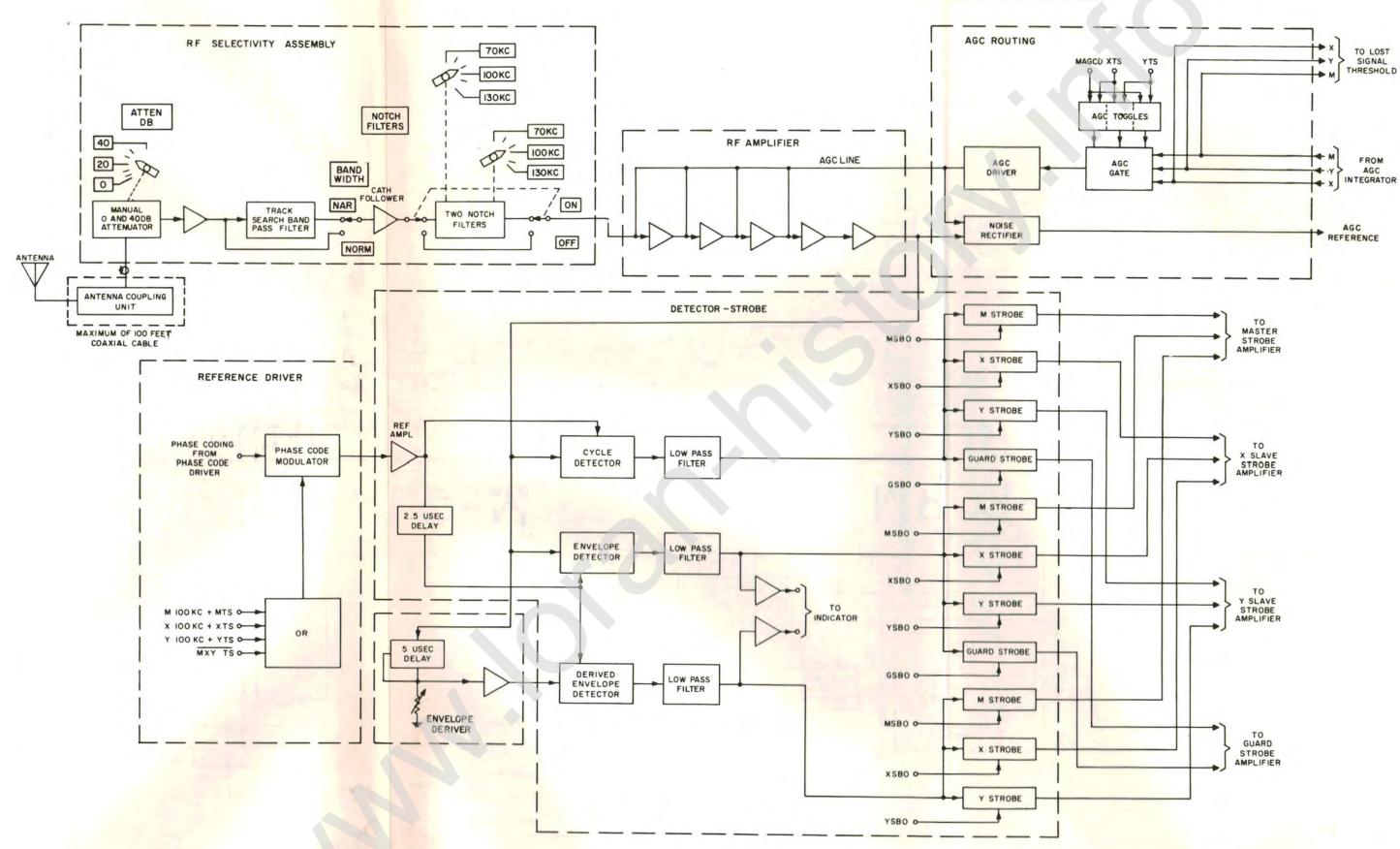

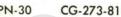

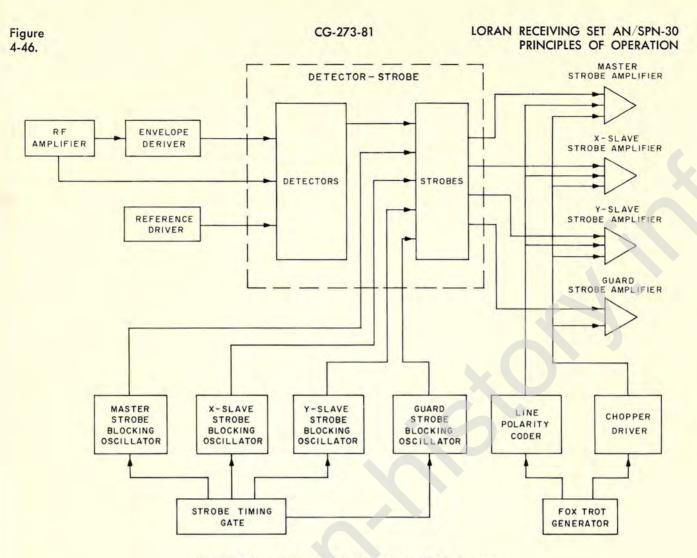

| 4-46.          | Detector-Strobe Section,<br>Block Diagram                                  | 4- 56          | 6-69.          | Error Threshold Detector (A1601 -<br>A1610), Test Setup           |   |

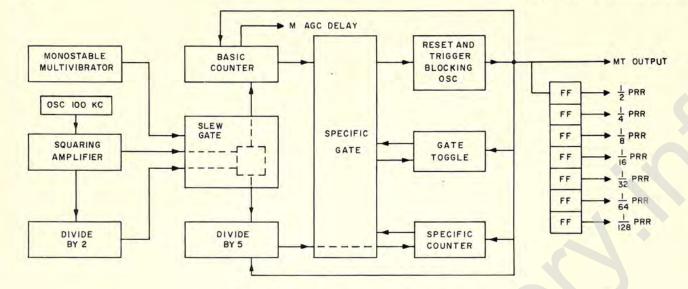

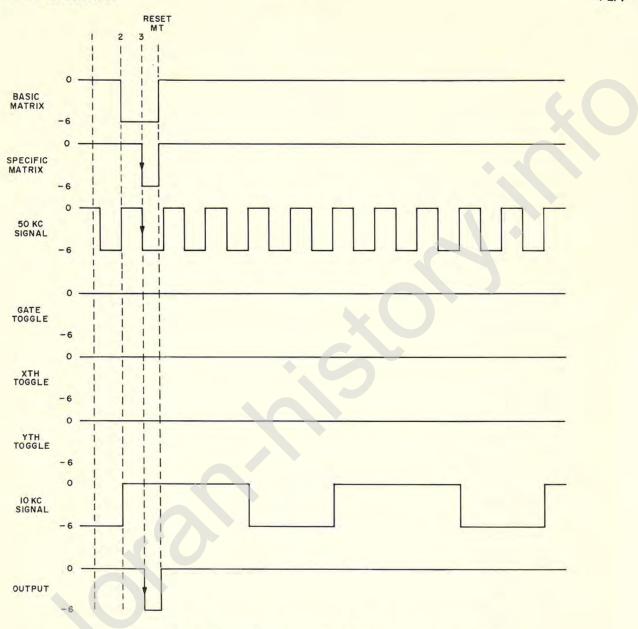

| 4-30.          | Diode Connections for Indicating<br>Sweep Time Determination Circuit.      | 4-38           | 4-17.          | 50- Kc and 10- Kc Signal Paths,<br>Block Diagram                  |   |

| 5-40.          | Diode Matrix (A1314), Parts                                                | 5-207          | 6-180.         | Filter Board (E1006), Schematic<br>Diagram.                       |   |

| 6-140.         | Location                                                                   | 6-169          | 6-4.           | 500- Microsecond Spacing Conditions,<br>Waveform at A1304, TP2    |   |

| 6-54.<br>5-64. | Diode Matrix (A1314), Test Setup for.<br>Dither Oscillator (A2002, A2003), | 6-58           | 4-8.           | Four-Line Diode Matrix,<br>Block Diagram                          |   |

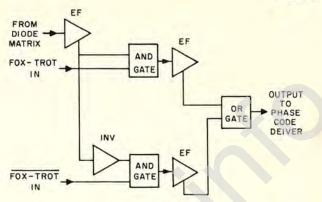

|                | Parts Location<br>Dither Oscillator (A2002, A2003),                        | 5-237          | 4-56.<br>5-48. | Fox-Trot Generator, Block Diagram.<br>Fox-Trot Generator (A1322), |   |

|                | Schematic Diagram                                                          | 6-217          |                | Parts Location                                                    | - |

| 6-76.          | Dither Oscillator (A2002, A2003),<br>Test Setup                            | 6-92           |                | Fox-Trot Generator (A1322),<br>Schematic Diagram                  | 1 |

| 4-83.          | Dither Oscillator Torque versus<br>Error Voltage                           | 4-83           | 6-59.          | Fox-Trot Generator (A1322),<br>Test Setup for                     |   |

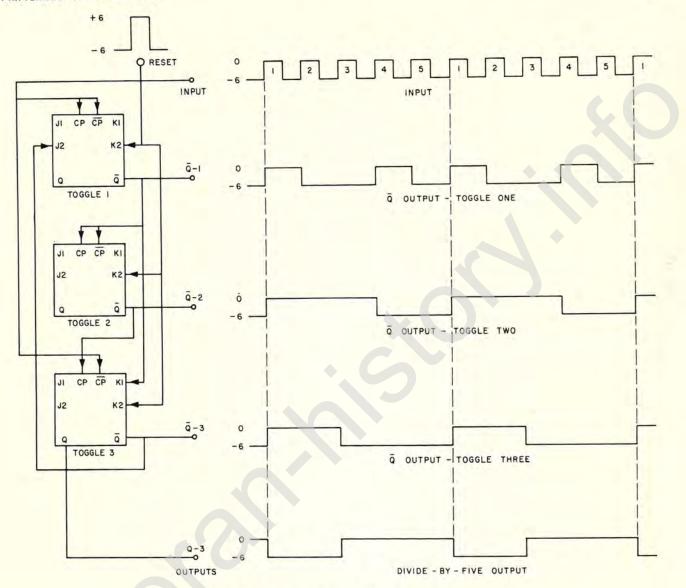

| 4-24.          | Divide-by-5, Block Diagram                                                 | 4-29           | 4-57.          | Fox-Trot Generator, Waveshapes                                    |   |

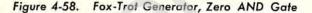

| 6-37.          | Dynamic Range Curve, Typical                                               | 6-42           | 4-58.          | Fox-Trot Generator, Zero AND Gate.                                |   |

| 6-33.          | Dynamic Range Test Setup,                                                  |                | 4-59.          | Fox-Trot Generator, Zero OR Gate                                  |   |

| 6-175.         | Block Diagram<br>E1001, Assembly Board,                                    | 6-38           | 6-32.          | Frequency Response Test Setup,<br>Block Diagram                   |   |

|                | Schematic Diagram<br>E1002, Basic Matrix Board,                            | 6-239          | 6-15.          | Gain Control, Temporary Connec-<br>tions, Common to All Intervals |   |

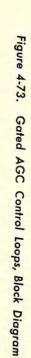

| 6-177.         | Schematic Diagram<br>E1003, Relay Board, Schematic                         | 6-241          | 4-73.          | Gated AGC Control Loops,<br>Block Diagram                         |   |

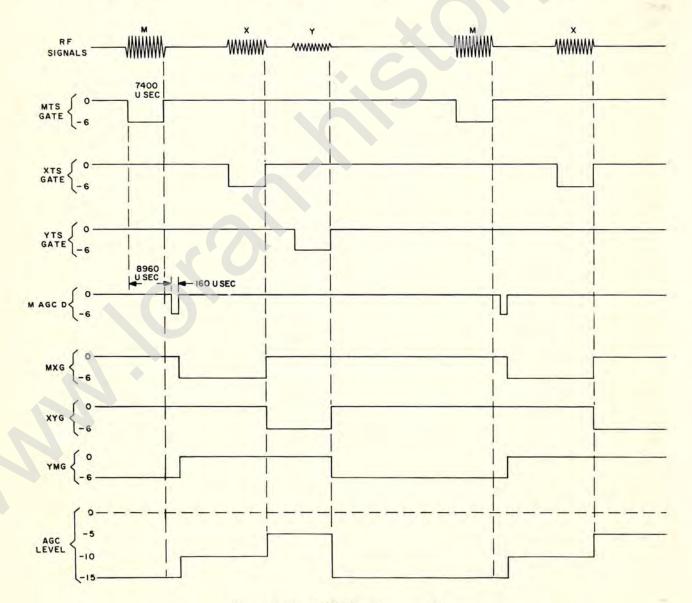

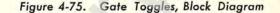

|                | Diagram                                                                    | 6-243          | 4-75.          | Gate Toggles, Block Diagram                                       |   |

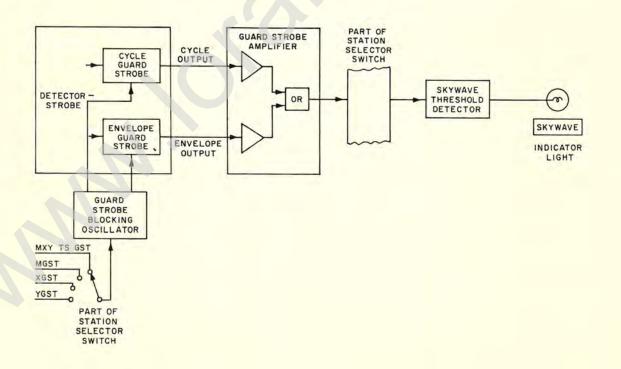

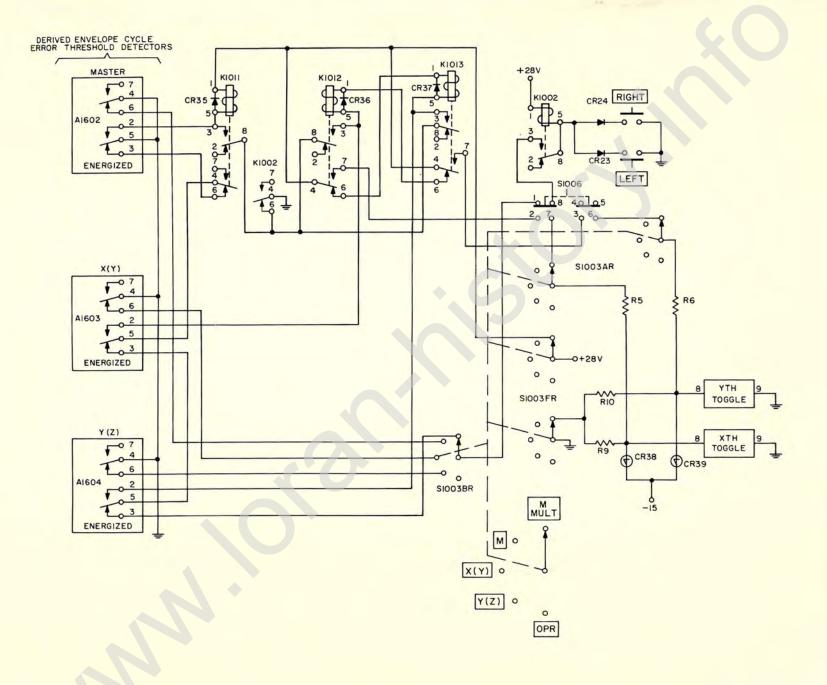

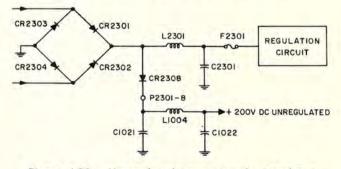

| 0-178.         | E1004, Assembly Board, Schematic<br>Diagram                                | 6-245          | 4-86.<br>4-61. | Guard Signal Path, Block Diagram<br>Guard Strobe Action           |   |

| 6-179.         | E1005, Relay Board, Schematic<br>Diagram.                                  | 6-247          | 5-25.          | Guard Strobe Amplifier Module<br>(A601), Parts Location           |   |

| 6-180.         | E1006, Filter Board, Schematic<br>Diagram                                  | 6-249          | 6-126.         | Guard Strobe Amplifier Module<br>(A601), Schematic Diagram        |   |

| 6-181.         | E1007, Logic Board, Schematic                                              | 6-251          | 6-41.          | Guard Strobe Amplifier Module                                     |   |

| 5-39.          | Diagram<br>Encoder Driver (A1215), Parts                                   |                | 4-72.          | (A601), Test Setup                                                |   |

| 6-139.         | Location                                                                   | 5-206          | 5-66.          | High Voltage Power Supply Module<br>(A2301), Parts Location       |   |

| 6-74.          | Schematic Diagram<br>Encoder Test Circuit, Slave Delay                     | 6-167          | 6-166.         | High Voltage Power Supply Module<br>(A2301), Schematic Diagram    |   |

| 5-24.          | Servo Module (A2001, A2101)<br>Envelope Deriver Module (A501),             | 6-83           | 6-78.          | High Voltage Power Supply Module<br>(A2301), Test Setup           |   |

|                | Parts Location<br>Envelope Deriver Module (A501),                          | 5-172          | 4-30.          | Indicator Sweep Time Determination<br>Circuit, Diode Connections  |   |

|                | Schematic Diagram<br>Envelope Deriver Module (A501),                       | 6-139          | 2-8.           | Interconnecting Diagram, Loran<br>Receiving Set AN/SPN-30         |   |

|                | Test Setup                                                                 | 6-45           | 6-1.           | Interference Signal Source                                        |   |

| 5-17.          | Envelope Deriver Module (A501),<br>Voltage and Resistance Measure-         |                | 6-17.          | Line Polarity Coder (A2701), Non-<br>Synchronous Point at TP1     |   |

| 4-50.          | Envelope Detector Output with Input                                        | 5-157          | 5-70.          | Line Polarity Coder Module (A2701),<br>Parts Location             |   |

|                | in Phase                                                                   | 4- 57<br>4- 85 | 6-170.         | Line Polarity Coder (A2701),                                      |   |

| 4-84.          | Envelope Loops, Block Diagram                                              | 4-00           | 6 01           | Schematic Diagram                                                 |   |

| 5-58.          | Error Amplifier (A1613 - A1619),<br>Parts Location                         | 5-229          | 6-81.          | Line Polarity Coder (A2701), Test<br>Setup                        |   |

| 6-158.         | Error Amplifier (A1613 - A1619),<br>Schematic Diagram                      | 6-205          | 6-46.          | Lissajous Patterns for Adjustment of<br>100-Kc Driver (A801)      |   |

| viii           |                                                                            |                |                |                                                                   | 0 |

0

# INDEX OF ILLUSTRATIONS (Cont)

| Figure         |                                                                         | Page         | Figure         |                                                                      | Page         |

|----------------|-------------------------------------------------------------------------|--------------|----------------|----------------------------------------------------------------------|--------------|

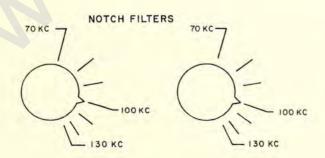

| 6-51.          | Lissajous Patterns for Alignment of<br>10-Kc Resolver Driver (A934)     | 6- 55        | 4-10.<br>5-27. | Notch Rejection Diagram<br>100-kc Driver Module (A801), Parts        | 4-16         |

| 6-2.           | Lissajous Patterns for 100-Kc<br>Resolver Driver                        | 6-5          |                | Location                                                             | 5-177        |

| 6-181.         | Logic Board (E1007), Schematic<br>Diagram.                              | 6-251        | 6-45.          | Schematic Diagram                                                    | 6-145        |

| 6-29.          | Logic Noise, Sample of Excessive,<br>at Input to Specific Gate (A931)   | 6-31         | 5- 5.          | Setup for                                                            | 6-49         |

| 5-65.          | Low Voltage Power Supply Module<br>(A2201), Parts Location              | 5-238        | 0 0.           | Servos, and 100-kc Driver,<br>Servicing Diagram                      | 5-135        |

| 6-165.         | Low Voltage Power Supply Module<br>(A2201), Schematic Diagram           | 6-219        | 6-44.          | 100-kc Reference Oscillator, Adjust-<br>ments, Cover for Making.     | 6-48         |

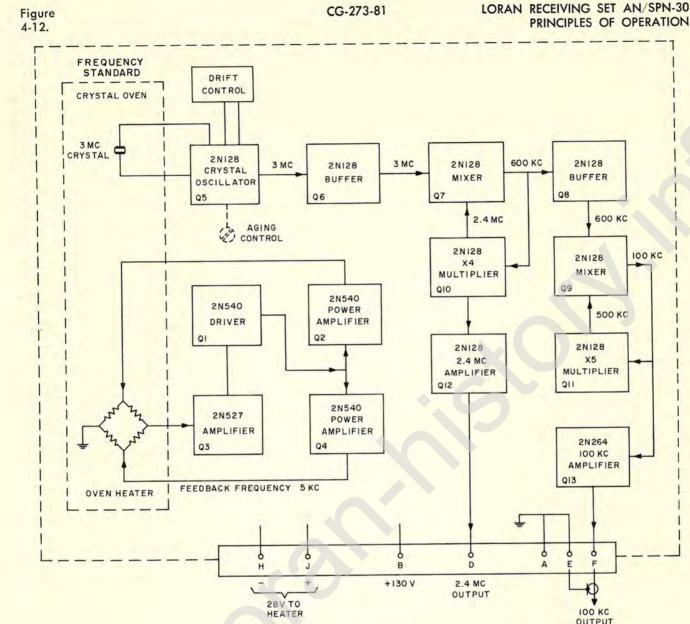

| 6-77.          | Low Voltage Power Supply Module                                         | 6-93         | 4-12.          | 100-kc Reference Oscillator, Block                                   | 4-18         |

| 6-174.         | (A2201), Test Setup<br>Magnetic Amplifier, Schematic                    |              | 6-43.          | Diagram.<br>100-kc Reference Oscillator,                             | 4-10         |

| 5-61.          | Diagram.<br>Master Cycle Servo Module (A1801),                          | 6-237        | 5 96           | Connection of Trimming<br>Capacitor to                               | 6-47         |

| 6-161.         | Parts Location<br>Master Cycle Servo Module (A1801),                    | 5-232        | 5-26.          | 100-kc Reference Oscillator Module<br>(A701), Parts Location         | 5-175        |

| 6-72.          | Schematic Diagram<br>Master Cycle Servo Module (A1801),                 | 6-211        |                | 100-kc Reference Oscillator Module<br>(A701), Schematic Diagram      | 6-143        |

| 5-62.          | Test Setup<br>Master Envelope Servo Module                              | 6-80         |                | 100-kc Reference Oscillator Module<br>(A701), Terminal Connections   | 6-47         |

|                | (A1901), Parts Location                                                 | 5-233        | 4-11.          | 100-kc Signal Path, Block Diagram                                    | 4-17         |

| 6-162.         | Master Envelope Servo Module                                            | 0.010        | 4-16.          | 100-kc Resolvers, Block Diagram                                      | 4-22         |

| 6-73.          | (A1901), Schematic Diagram<br>Master Envelope Servo Module              | 6-213        | 0-191.         | Operational Amplifier Module (A1451-<br>A1453), Schematic Diagram    | 6-191        |

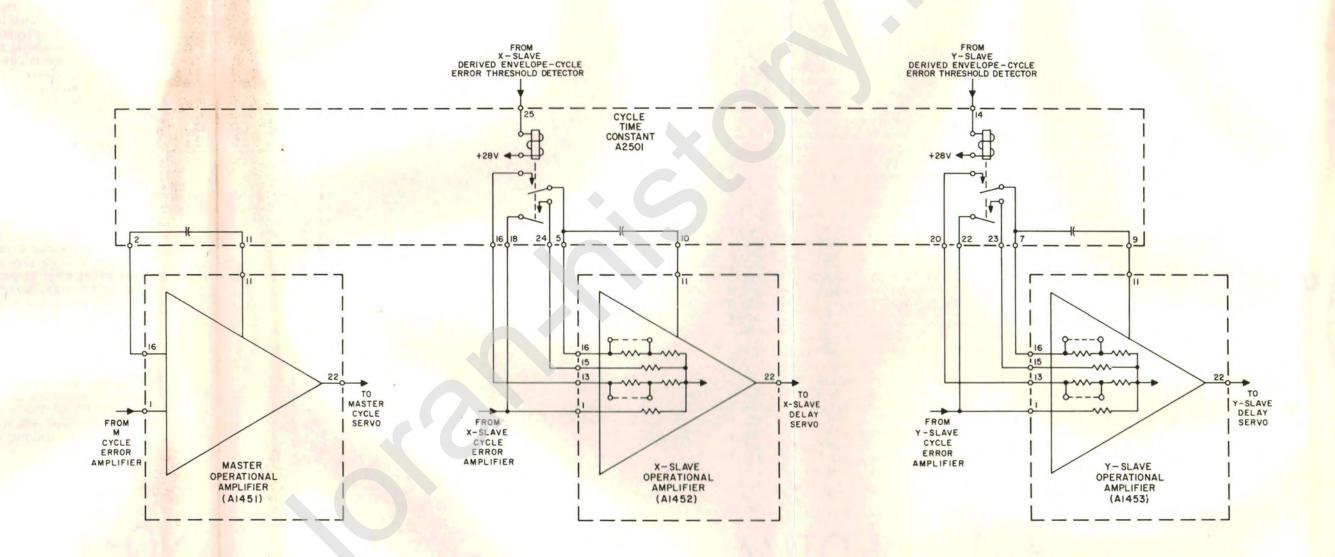

| 4- 87.         | (A1901), Test Setup<br>Master Multiple, Simplified Sche-                | 6-82         | 4-80.          | Operation Amplifiers - Cycle Time<br>Constant, Simplified Functional | 0-101        |

|                | matic Diagram                                                           | 4-92         |                | Block Diagram                                                        | 4-81         |

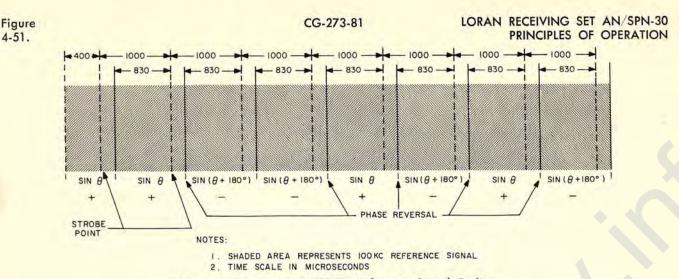

| 4-51.          | Master-1 100-kc Reference Signal                                        | 1            | 5-51.          | Operational Amplifier Module (A1451-                                 |              |

| 4 00           | Coding                                                                  | 4-58         | 0 00           | A1453), Parts Location                                               | 5-221        |

| 4-39.<br>3-11. | Matrix Output for Code Logic Gates .<br>Module Location, Bottom Drawer, | 4-49         | 6-63.          | Operational Amplifier Module<br>(A1451-A1453), Test Setup            | 6-69         |

| 0.14           | First Channel                                                           | 3-26         | 2-3.           | Outline Drawing.                                                     | 2-3          |

| 3-14.          | Module Location, Bottom Drawer,                                         | 3-29         | 4-2. 6-121.    | Overall Block Diagram                                                | 4-5<br>6-119 |

| 3-12.          | Fourth and Fifth Channels<br>Module Location, Bottom Drawer,            | 3-29         | 4-45.          | Overall Wiring Diagram Peak Detector, Partial Schematic              | 0-119        |

| 0-14.          | Second Channel                                                          | 3-27         | 1- 10.         | Diagram                                                              | 4-55         |

| 3-13.          | Module Location, Bottom Drawer,                                         |              | 5-42.          | Phase Code Driver (A1316), Parts                                     | 1 00         |

| 3-10.          | Third Channel<br>Module Location, Top Drawer                            | 3-28<br>3-25 | 6-142.         | Location                                                             | 5-209        |

| 5-35.          | Monostable Multivibrator (A940,<br>A1313), Parts Location               | 5-186        | 6-39.          | Diagram                                                              | 6-173        |

| 6-136.         | Monostable Multivibrator (A940,<br>A1313), Schematic Diagram            | 6-161        |                | Envelope Channel in A401,<br>Oscilloscope Display                    | 6-45         |

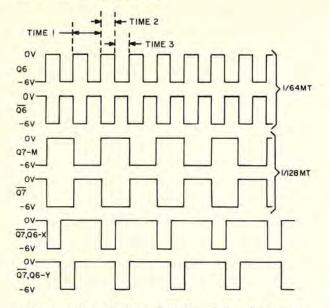

| 4-43.          | M, X, and Y Signal Development in                                       | 0-101        | 6-19.          | Phase Shift Network, Standard, for                                   | 0-10         |

|                | the Skywave Time Sharing Gate                                           | 4-53         |                | Cycle Servo Gain Elevation                                           | 6-20         |

| 5-69.          | Noise Generator (A2601), Parts                                          | 5 947        | 6-10.          | Phase Switching Points, Possible, in<br>Pulses at TP2 of Reference   |              |

| 6 160          | Location                                                                | 5-247        |                | Driver (A2703)                                                       | 6-14         |

| 0-109.         | Diagram                                                                 | 6-227        | 4-64.          | Phasing Control of Detector-Strobe                                   |              |

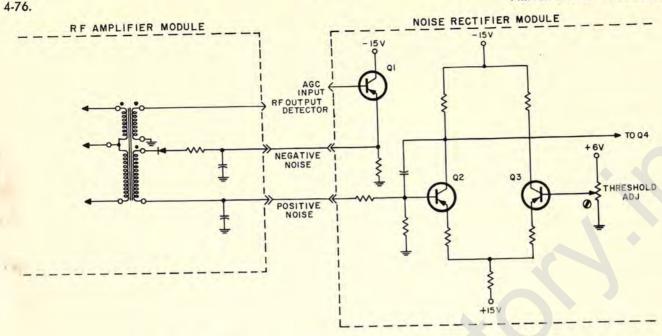

| 4-76.          | Noise Rectifier Circuit, Partial                                        | 1.111        |                | Unit                                                                 | 4-67         |

| 5-53.          | Schematic Diagram<br>Noise Rectifier (A1505), Parts                     | 4-76         | 4-40.<br>6-6.  | Polarity Encoder, Block Diagram<br>Polarity Encoder, Output Phase    | 4-49         |

|                | Location                                                                | 5-224        |                | Coding                                                               | 6-10         |

| 0-193.         | Noise Rectifier (A1505), Schematic<br>Diagram.                          | 6-195        | 5-47.          | Polarity Encoder (A1321), Parts<br>Location                          | 5-214        |

| 6-65.          | Noise Rectifier (A1505), Test Setup                                     | 6-71         | 6-147.         | Polarity Encoder (A1321), Schematic<br>Diagram.                      | 6-183        |

| 6-31.          | Notch Filter Test and Alignment<br>Setup, Block Diagram                 | 6-37         | 6-58.          | Polarity Encoder (A1321), Test<br>Setup for                          | 6-63         |

| 6-34.          | Notch Filter Tracking Test Setup,<br>Block Diagram                      | 6-39         | 6-5.           | Polarity Encoder, Waveform at<br>A1321, TP1.                         | 6-9          |

| ORIGIN         |                                                                         |              |                | a subscription of the second of                                      | ix           |

|                |                                                                         |              |                |                                                                      |              |

# INDEX OF ILLUSTRATIONS (Cont)

| Figure         |                                                                       | Page         | Figure          |                                                                          | Page          |

|----------------|-----------------------------------------------------------------------|--------------|-----------------|--------------------------------------------------------------------------|---------------|

| 5-13.          | Power Distribution, Servicing<br>Diagram                              | 5-151        | 5-15.           | R-f Selectivity Module (A201), Voltage<br>and Resistance Measurements    | 5-155         |

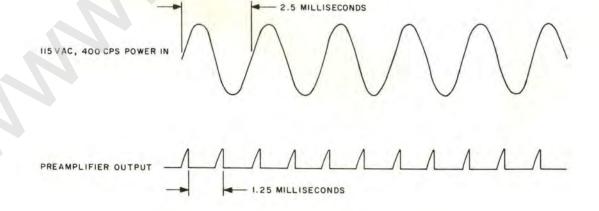

| 4-81.<br>6-57. | Preamplifier Output, Waveshapes<br>Pulse Generator Output for Testing | 4-82         | 5-12.           | Sequence Control, Servicing<br>Diagram.                                  | 5-149         |

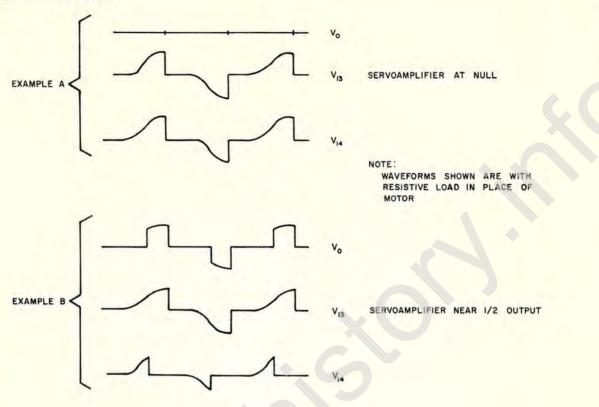

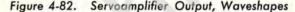

|                | Slew Limit (A1320)                                                    | 6-63         | 4-82.           | Servoamplifier Output, Waveshapes                                        | 4-83          |

| 5-44.          | Pulse Group Timing Gate (A1318),                                      | 5 911        | 4-52.           | Shifting Crossover Point by Wave-                                        | 4-59          |

| 6-144.         | Parts Location<br>Pulse Group Timing Gate (A1318),                    | 5-211        | 4-85.           | form Addition                                                            | 4-00          |

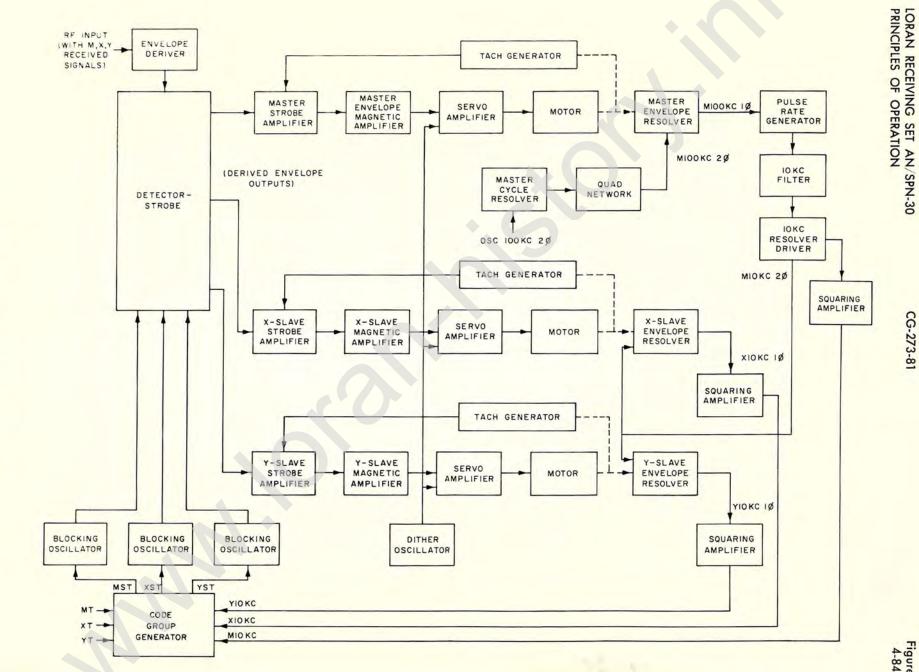

|                | Schematic Diagram                                                     | 6-177        |                 | Time Relationships                                                       | 4-86          |

| 4-25.          | Pulse Rate Generator, Block                                           | 4.00         | 4-42.           | Skywave Time Sharing Gate, AND                                           | 1 50          |

| 5-8.           | Diagram<br>Pulse Rate Generator, Servicing                            | 4-32         | 4-43.           | Gates in<br>Skywave Time Sharing Gate, M, X,                             | 4-52          |

|                | Diagram                                                               | 5-141        |                 | and Y Signal Development in                                              | 4-53          |

| 5-20.          | Receiver Cabinet (A101), Parts                                        |              | 5-45.           | Skywave Time Sharing Gate (A1319),                                       | 5 010         |

| 5-59.          | Location                                                              | 5-159        | 6-145           | Parts Location<br>Skywave Time Sharing Gate (A1319),                     | 5-212         |

| 0.00.          | Parts Location                                                        | 5-230        | 0-110.          | Schematic Diagram                                                        | 6-179         |

| 6-159.         |                                                                       |              | 6-55.           | Skywave Time Sharing Gate (A1319),                                       |               |

| 4-69.          | Schematic Diagram<br>Rectification by Use of Mechanical               | 6-207        | 6-74.           | Test Setup for                                                           | 6-62          |

| 1-00.          | Switching                                                             | 4-69         | 0-14.           | A2101), Encoder Test Circuit                                             | 6-83          |

| 5-72.          | Reference Driver (A2703), Parts                                       |              | 5-63.           | Slave Delay Servo Module (A2001,                                         |               |

| 6-172.         | Location                                                              | 5-250        | 6 162           | A2101), Parts Location<br>Slave Delay Servo Module (A2001,               | 5-234         |

| 0-112.         | Diagram.                                                              | 6-233        | 0-105.          | A2101), Schematic Diagram                                                | 6-215         |

| 6-83.          | Reference Driver (A2703), Test                                        |              | 6-75.           | Slave Delay Servo Module (A2001,                                         |               |

| 6-9.           | Setup                                                                 | 6-98<br>6-14 | 5 94            | A2101), Test Circuit.                                                    | 6-85<br>5-185 |

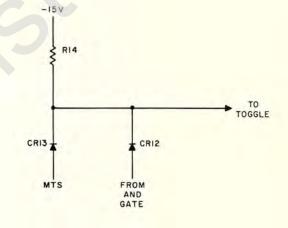

| 4-60.          | Reference Driver Waveforms Reference Driver, Waveshapes               | 4-64         | 5-34.<br>6-135. | Slew Gate (A939), Parts Location<br>Slew Gate (A939), Schematic          | 5-105         |

| 6-177.         |                                                                       |              |                 | Diagram                                                                  | 6-159         |

| 0 100          | Diagram.                                                              | 6-243        | 6-52.           | Slew Gate (A939), Test Setup for                                         | 6-55          |

| 0-179.         | Relay Board (E1005), Schematic<br>Diagram                             | 6-247        | 4-23.<br>6-8.   | Slew Gate, Timing Waveshapes<br>Slew Gate, Waveform at A939, TP2         | 4-27<br>6-12  |

| 5-30.          | Reset Blocking Oscillator (A932,                                      |              | 5-46.           | Slew Limit (A1320), Parts Location.                                      | 5-213         |

| 6 191          | A1312), Parts Location                                                | 5-181        | 6-146.          |                                                                          | 0 101         |

| 6-131.         | Reset Blocking Oscillator (A932, A1312), Schematic Diagram            | 6-151        | 6-56.           | Diagram                                                                  | 6-181<br>6-63 |

| 4-35.          | Reset Function Diagram for 8-Pulse                                    |              | 4-44.           | Slew Limit, Waveforms                                                    | 4-54          |

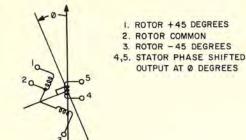

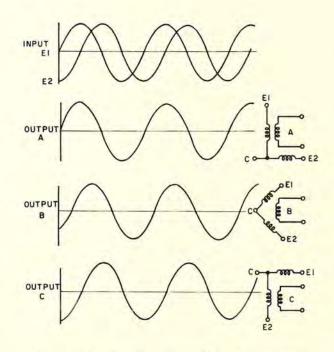

| 4-14.          | or Single-Pulse Operation<br>Resolver Phase-Shift Characteristics     | 4-45<br>4-20 | 4-29.<br>5-29.  | Specific Counter, Block Diagram                                          | 4-37<br>5-180 |

| 4-15.          | Resolver, Typical Connection                                          | 4-20         | 6-130.          | Specific Gate (A931), Parts Location.<br>Specific Gate (A931), Schematic | 5-180         |

| 4-13.          | Resolver, Typical Schematic Repre-                                    |              |                 | Diagram                                                                  | 6-149         |

| 6 11           | sentation of<br>R-f Amplifier and Associated                          | 4-20         | 6-48.           | Specific Gate (A931), Test Setup for .                                   | 6-52          |

| 6-11.          | Circuitry, Test Setup                                                 | 6-15         | 6-28.           | Specific Gate, Waveform at<br>A931, TP2                                  | 6-30          |

| 5-22.          | R-f Amplifier Module (A301), Parts                                    |              | 4-28.           | Specific Gate Waveshapes, S-5                                            |               |

| 6 1.93         | Location                                                              | 5-164        | 1 97            | Rate (49,500 microseconds)                                               | 4-36          |

| 0-125.         | R-f Amplifier Module (A301),<br>Schematic Diagram                     | 6-135        | 4-27.           | Specific Gate Waveshapes, S-7<br>Rate (49,300 microseconds)              | 4-35          |

| 5-16.          | R-f Amplifier Module (A301), Voltage                                  |              | 5-33.           | Squaring Amplifier (A935-A938),                                          |               |

| 6-35.          | and Resistance Measurements<br>R-f Amplifier Test Setup, Block        | 5-156        | 6 194           | Parts Location                                                           | 5-184         |

| 0-00.          | Diagram.                                                              | 6-40         | 0-134.          | Squaring Amplifier (A935-A938),<br>Schematic Diagram                     | 6-157         |

| 5-4.           | R-f and Detector Section, Servicing                                   |              | 4-53.           | Squeegee Output Stage, Partial                                           |               |

| 6 1 0          | Diagram.                                                              | 5-133        | 4 71            | Schematic Diagram                                                        | 4-61          |

| 6-18.          | R-f Filter Assembly for Use with<br>Kintel DC VTVM                    | 6-19         | 4-71.           | Strobe Amplifier, Diode Gate<br>Switching Circuit                        | 4-70          |

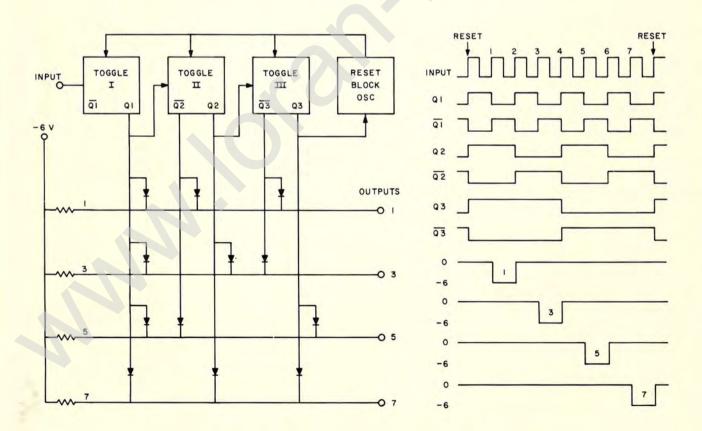

| 4-9.           | R-f Selectivity Curve                                                 | 4-15         | 6-13.           | Strobe Amplifier Input Waveforms                                         | 6-17          |

| 5-21.          | R-f Selectivity Module (A201),                                        | 5 160        | 5-50.           | Strobe Amplifier Module (A1405-                                          | 5 915         |

| 6-122.         | Parts Location                                                        | 5-160        | 6-150.          | A1407), Parts Location<br>Strobe Amplifier Module (A1405-                | 5-217         |

| the second     | Schematic Diagram                                                     | 6-133        | 0.000           | A1407), Schematic Diagram                                                | 6-189         |

|                |                                                                       |              |                 |                                                                          |               |

x

# INDEX OF ILLUSTRATIONS (Cont)

| 6-3.Strobe Amplifier Output Waveforms,<br>Typical5-1.Test Point Location, Top Drawer5-6.4-65.Strobe Amplifier, Simplified Sche-<br>matic Diagram6-74-3.Three-Stage Binary Counter,<br>Waveshapes4-116-62.Strobe Amplifier (A1405-A1407),<br>Test Setup6-674-4.Three-Stage Binary Counter,<br>Waveshapes4-125-10.Strobe Amplifier (A1405-A1407),<br>Afoth (A1404), Strobe Blocking Oscillator (A1401-<br>A1404), Parts Location5-1454-18.Toggle Diode Gating with a<br>Decreasing Input.4-245-49.Strobe Blocking Oscillator (A1401-<br>A1404), Strobe Blocking Oscillator, Test<br>Setup for5-1664-21.Toggle External Gate Switching with<br>QI Off.4-22.6-60.Strobe Blocking Oscillator, Test<br>Setup for6-1874-22.Toggles, M, X, and Y, Waveshapes4-466-61.Strobe Blocking Oscillator, Test<br>Location6-210.Strobe Blocking Oscillator, Test<br>Diagram.6-1674-21.Toggles, M, X, and Y, Waveshapes4-476-20.Strobe Sampling Point Determination<br>Diagram.6-210.5-210.A1501-A1503, Schematic Diagram.6-1756-43.Strobe Timing Gate, Waveshapes4-51.6-167.28. Voit Power Supply Module<br>(A2401), Parts Location.5-2436-132.10- kc Filter (A933), Parts Location<br>Diagram.5-1836-167.24.2001 Power Supply Module<br>(A2401), Parts Location.5-2436-43.Strobe Timing Gate, Waveshapes4-51.6-167.28. Voit Power Supply Module<br>(A2401), Parts Location6-223<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure   |                                     | Page  | Figure |                                     | Page  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------|-------|--------|-------------------------------------|-------|

| 4-65.       Strobe Amplifier, Simplified Schematic Diagram       4-67       Horsen and the probability of t | 6-3.     |                                     |       |        |                                     | 5-6   |

| 4-65.       Strobe Amplifier, Simplified Schematic Diagram       4-67         6-62.       Strobe Amplifier, (A1405-A1407),<br>Test Setup       4-67       4-4.       Hirree-Stage Binary Counter,<br>Waveshapes       4-12         6-62.       Strobe Amplifier, Integrators, and<br>ACC, Servicing Diagram       6-67       4-18.       Toggle Circuit, Basic Simplified<br>Schematic Diagram       4-24         5-49.       Strobe Blocking Oscillator (A1401-<br>A1404), Schematic Diagram       5-216       4-20.       Toggle External Gate Switching with a<br>Increasing Input.       4-25         6-12.       Strobe Blocking Oscillator (A1401-<br>A1404), Schematic Diagram       6-187       4-21.       Toggle External Gate Switching with<br>Q1 Off       4-25         6-60.       Strobe Blocking Oscillator, Test<br>Setup for       6-187       4-36.       Toggle External Gate Switching with<br>Q1 Off       4-26         6-61.       Strobe Blocking Oscillator, C1401-<br>A1404), Waveforms       6-66       4-37.       Toggle External Gate Switching with<br>Q1 Off       4-25         6-62.       Strobe Blocking Oscillator, C1401-<br>A1404, Waveforms       6-66       4-37.       Toggle External Gate Switching with<br>Q1 Off       4-26         6-63.       Strobe Blocking Oscillator, C1401-<br>A1404, Waveforms       6-66       4-37.       Toggle Cayo, A30, A1310, A1310,<br>A1404, Waveforms       6-66         6-161.       Strobe Simplified Schematic<br>D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | Typical                             | 6-7   | 4-3.   | Three-Stage Binary Counter,         |       |

| matic Diagram4-674-4.Three Stage Binary Counter,<br>Waveshapes6-62.Strobe Amplifier (A1405-A1407),<br>Test Setup6-67Toggle Circuit, Basic Simplified<br>Schematic Diagram4-125-10.Strobe Amplifiers, Integrators, and<br>AGC, Servicing Diagram5-145Toggle Diode Gating with a<br>Decreasing Input4-245-49.Strobe Blocking Oscillator (A1401-<br>A1404), Parts Location5-2164-18.Toggle Diode Gating with a<br>Decreasing Input4-256-140.Strobe Blocking Oscillators,<br>Triggers for6-1874-22.Toggle External Gate Switching with<br>QI Off.4-264-54.Strobe Blocking Oscillator, Test<br>Strobe Blocking Oscillator, Test<br>Diagram.6-1674-21.Toggles, M, X, and Y, Block<br>Diagram.4-466-20.Strobe Slocking Oscillator (A1401-<br>A1404), Waveforms6-666-676-674-37.Toggles, M, X, and Y, Waveshapes -<br>4-614-147.6-20.Strobe Blocking Oscillator (A1401-<br>Diagram.6-666-143.5-2106-120.5-2106-143.Strobe Timing Gate (A1317), Parts<br>Location.6-216-167.6-175.6-167.28-Voit Power Supply Module<br>(A2401), Parts Location.5-1826-132.10-ke Filter (A933), Schematic<br>Diagram.6-153.6-167.6-167.28-Voit Power Supply Module<br>(A2401), Parts Location.6-2146-133.10-ke Filter (A933), Schematic<br>Diagram.6-153.6-167.6-167.6-167.6-167.6-167.6-167.6-133.10-ke Resolver Driver (A934), Schemat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-65.    | Strobe Amplifier, Simplified Sche-  |       |        | Block Diagram                       | 4-11  |

| 6-62.       Strobe Amplifier (A1405-A1407),<br>Test Setup       6-67       Waveshapes       4-12         5-10.       Strobe Amplifiers, Integrators, and<br>AGC, Servicing Diagram       6-67       4-18.       Toggle Circuit, Basic Simplified<br>Schematic Diagram       4-24         6-49.       Strobe Blocking Oscillator (A1401-<br>A1404), Strobe Blocking Oscillators (A1401-<br>A1404), Schematic Diagram       6-16       4-20.       Toggle External Gate Switching with<br>QI 0ff       4-25         6-419.       Strobe Blocking Oscillators,<br>Triggers for       6-16       4-21.       Toggle External Gate Switching with<br>QI 0ff       4-26         6-60.       Strobe Blocking Oscillator, Test<br>Setup for       6-61       4-36.       Toggles, M, X, and Y, Block       4-46         6-61.       Strobe Blocking Oscillator, (A1401-<br>A1404), Waveforms       6-66       4-37.       Toggle (A901-A930, A1301-A1310,<br>A1404), Waveforms       6-66         6-51.       Strobe Sampling Point Determination<br>Diagram       6-20       Triggers for Strobe Blocking<br>Group at TP4       6-10       6-105       6-107       4-54.       Triggers for Strobe Blocking<br>Group at TP4       6-105       6-107       4-54.       Triggers for Strobe Blocking<br>Group at TP4       6-133       6-143.       10-kc Filter (A933), Schematic<br>Diagram       6-135       6-107       6-107       6-107       6-107       6-107       6-108       6-107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | matic Diagram                       | 4-67  | 4-4.   |                                     |       |

| Test Setup       6-67       4-18       Toggle Circuit, Basic Simplified         5-10.       Strobe Amplifiers, Integrators, and       Schematic Diagram       4-24         AGC, Servicing Diagram       5-145       4-19       Toggle Diode Gating with a       4-25         5-49.       Strobe Blocking Oscillator (Al401-       5-216       4-20       Toggle Diode Gating with a       4-25         6-12.       Strobe Blocking Oscillator (Al401-       6-16       4-21.       Toggle External Gate Switching with       4-25         6-149.       Strobe Blocking Oscillators,       6-187       4-21.       Toggle External Gate Switching with       4-25         6-60.       Strobe Blocking Oscillator, Test       6-187       4-21.       Toggle Strobe, M. X, and Y, Block       4-26         6-61.       Strobe Blocking Oscillator (Al401-       6-66       Al501-Al503), Parts Location       5-179         4-55.       Strobe Gate, Simplified Schematic       6-66       Al501-Al503), Parts Location       5-179         6-13.       Torbe Sampling Point Determination       6-20.       Strobe Timing Gate (Al317), Parts       6-210       Toggle (A901-A930, Al301-Al310,       6-147         6-143.       Strobe Timing Gate (Al317), St Code       6-175       6-167       28-Voit Power Supply Module       6-51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-62.    |                                     |       |        | Waveshapes                          | 4-12  |

| 5-10.       Strobe Amplifiers, Integrators, and<br>AGC, Servicing Diagram.       5-145       Schematic Diagram.       4-24         AGC, Servicing Oscillator (A1401-<br>A1404), Parts Location       5-216       4-19.       Toggle Diode Gating with a<br>Decreasing Input.       4-25         6-12.       Strobe Blocking Oscillator Pulses at<br>TP2 of A1401 through A1404.       6-16       4-20.       Toggle Diode Gating with a<br>Decreasing Input.       4-25         6-149.       Strobe Blocking Oscillator A1404.       6-16       4-21.       Toggle External Gate Switching with<br>Q1 Off.       4-25         4-54.       Strobe Blocking Oscillators,<br>Triggers for       4-61       4-36.       Toggle external Gate Switching with<br>Q1 On       4-26         6-60.       Strobe Blocking Oscillator, Test       6-66       4-37.       Toggle (A901-A930, A1301-A1310,<br>A1501-A1503), Parts Location       5-179         6-51.       Strobe Sampling Point Determination<br>Diagram.       6-20.       Strobe Timing Gate (A1317), Parts<br>Location       6-210       Toggle (A901-A930, A1301-A1310,<br>A1501-A1503), Stest Setup for       6-51         6-7.       Strobe Timing Gate (A1317), Sthe-<br>matic Diagram       6-175       6-107.       28-Volt Power Supply Module<br>(A2401), Parts Location       5-244         6-133.       10- kc Filter (A933), Test Setup for       6-153       6-167.       28-Volt Power Supply Module<br>(A2401), Parts Location       5-244                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10.000 C |                                     | 6-67  | 4-18.  | Toggle Circuit, Basic Simplified    |       |

| AGC, Servicing Diagram.5-1454-19.Toggle Diode Gating with a<br>Decreasing Input.4-25 $5-49.$ Strobe Blocking Oscillator (A1401-<br>A1404), Schematic Diagram.5-2164-20.Toggle Diode Gating with a<br>Decreasing Input.4-25 $6-12.$ Strobe Blocking Oscillator (A1401-<br>A1404), Schematic Diagram.6-164-21.Toggle External Gate Switching with<br>QI Off.4-25 $4-54.$ Strobe Blocking Oscillator, (A1401-<br>A1404), Waveforms.6-1874-22.Toggle External Gate Switching with<br>QI Off.4-26 $6-60.$ Strobe Blocking Oscillator, (A1401-<br>A1404), Waveforms.6-664-36.Toggles, M, X, and Y, Buck<br>Diagram.4-46 $6-51.$ Strobe Blocking Oscillator (A1401-<br>A1404), Waveforms.6-664-37.Toggle (A901-A930, A1301-A1310,<br>A1501-A1503), Parts Location.5-179 $6-52.$ Strobe Banching Gate (A1317), Parts<br>Location.6-616-67.26-07.26-07.26-101 $6-143.$ Strobe Timing Gate (A1317), Stche-<br>matic Diagram.6-1756-167.28-Voit Power Supply Module<br>(A2401), Parts Location.5-244 $6-132.$ 10-kc Filter (A933), Arst Location5-1826-167.28-Voit Power Supply Module<br>(A2401), Parts Location.6-223 $6-133.$ 10-kc Resolver Driver (A934),<br>Parts Location5-1836-1556-167.28-Voit Power Supply Module<br>(A2401), Parts Location.6-223 $6-130.$ 10-kc Resolver Driver (A934),<br>Parts Location $6-155$ 6-167.8-100 Power Supply Module<br>(A2401), Parts Location.6-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-10     |                                     |       |        |                                     | 4-24  |

| 5-49.Strobe Blocking Oscillator (Al401-<br>Al404), Parts Location5-216Decreasing Input4-256-105-216Toggle Zideng with an<br>Increasing Input4-256-12.Strobe Blocking Oscillator Pulses at<br>Triggers for6-164-21.6-149.Strobe Blocking Oscillators,<br>Triggers for4-21.Toggle External Gate Switching with<br>QI Off4-25.6-60.Strobe Blocking Oscillator, Test<br>Setup for4-614-36.Toggles, M, X, and Y, Block4-26.6-61.Strobe Blocking Oscillator (Al401-<br>Al404), Waveforms6-664-37.Toggle (A901-A930, Al301-Al310,<br>Al501-Al503), Parts Location5-1796-53.Strobe Gate, Simplified Schematic<br>Diagram.6-616-62Al501-Al503), Schematic Diagram6-147.6-20.Strobe Sampling Point Determination<br>Diagram.6-215-210Al501-Al503), Test Setup for6-516-143.Strobe Timing Gate (Al317), Sche-<br>matic Diagram.6-1754-54.Triggers for Strobe Blocking<br>Oscillators.6-167.6-143.Strobe Timing Gate (Al317), Sche-<br>matic Diagram.6-1756-167.28-Volt Power Supply Module<br>(A2401), Parts Location5-2246-133.10-kc Filter (A933), Schematic<br>Diagram.6-1536-3.Typical Strobe Amplifier Output<br>Waveforms6-2236-131.10-kc Resolver Driver (A934),<br>Parts Location6-1556-121.Wiring Diagram.6-2136-10.6-1556-167.28-Volt Power Supply Module<br>(A2401) Test Setup.6-566-5136-131.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 10.    |                                     | 5-145 | 4.19   |                                     |       |